JTAG bietet mehr als nur Debugging und Programmierung

Sie sind eventuell mit JTAG vertraut, weil Sie bereits Tools mit einer JTAG-Schnittstelle verwendet haben. Bei Prozessoren wird JTAG häufig für den Zugriff zu ihren Debugging- und Emulationsfunktionen genutzt und bei allen FPGAs und CPLDs wird JTAG für den Zugang zu den Programmierfunktionen angewendet.

JTAG ist NICHT NUR eine Technologie für Prozessor-Debugging bzw. -Emulation.

JTAG ist NICHT NUR eine Technologie für die Programmierung von FPGAs/CPLDs.

Die Debugging- und Programmiertools, die üblicherweise mit JTAG verbunden werden, nutzen nur einen Aspekt der zugrunde liegenden Technologie – die Vierdraht-JTAG-Kommunikationsschnittstelle.

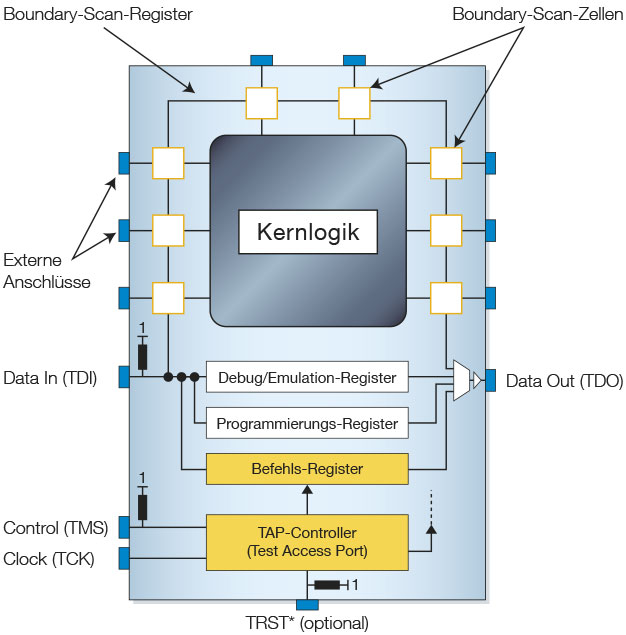

Diese vier Signale, zusammen bekannt als der Test Access Port oder TAP, sind Teil des Standards IEEE 1149.1. Dieser wurde entwickelt, um eine Technologie für das Testen bestückter Leiterplatten (Printed Circuit Board Assemblies – PCBAs) bereitzustellen – mit geringerem physischen Zugang im Vergleich zu Nadelbetttests und mit geringerem Aufwand für kundenspezifische Entwicklung, die für den Funktionstest notwendig ist. Der TAP wurde für die Interaktion mit neuen Registern entwickelt, mit denen Bausteine zur Implementierung dieses Testverfahrens ergänzt wurden.

Schon sehr schnell erkannten Siliziumhersteller die Vorteile der TAP-Nutzung für den Zugriff auf Register, die auch andere Funktionen bieten, wie z. B. Fehlersuche und Programmierung.

Das wichtigste Register, mit dem Bausteine speziell für den JTAG-Test ergänzt werden, wird Boundary-Scan-Register (BSR) genannt. Wie der Name schon verrät, befinden sich die einzelnen Bits oder Zellen dieses Registers am Umfang (Boundary) des Bausteins zwischen seiner Kernlogik und den Pins oder Lötperlen, über die er mit einer Leiterplatte verbunden ist. Der JTAG-Test wird häufig als Boundary-Scan bezeichnet.

.

Platinentest mit JTAG-Boundary-Scan

Boundary-Scan-Zellen (siehe oben) können zwei Betriebsarten haben. In ihrem Funktionsmodus haben sie keinen Einfluss auf die Funktion des Bausteins. Dies ist die Betriebsart für den Normalbetrieb der Platine. In ihrem Testmodus trennen sie die funktionelle Kernlogik des Bausteins von den Pins. Durch die Schaltung der Boundary-Scan-Zellen in den Testmodus können diese für die Kontrolle der Werte, die von einem aktivierten Baustein in ein Netz angesteuert werden, und für die Überwachung des Wertes dieses Netzes verwendet werden.

Die Trennung der Pin-Ansteuerung von der Funktionalität des aktivierten Bausteins macht die Boundary-Scan-Test-Entwicklung wesentlich einfacher als beim herkömmlichen Funktionstest, da für die Verwendung der Pins keine Gerätekonfiguration bzw. kein Booten erforderlich ist. Durch die Bereitstellung eines Mechanismus zur Ansteuerung und Überwachung aller aktivierten Signale auf einem Baustein über einen TAP mit vier Pins reduziert JTAG den für den Test einer Platine erforderlichen physikalischen Zugang beträchtlich.

Für die Anwendung dieser Boundary-Scan-Fähigkeit zur Prüfung einer Platine gibt es zwei Hauptverfahren. Das erste Verfahren, Verbindungstest (siehe nächster Abschnitt), liefert eine gute Testabdeckung, insbesondere bei Kurzschlüssen. Es basiert einzig und allein auf den JTAG-Fähigkeiten des Bausteins, den Verbindungen und Netzen auf der Platine und – bei XJTAG – auf der Logikfunktionalität der Platine. Das zweite Verfahren erweitert diese Abdeckung durch die Verwendung von JTAG-fähigen Bausteinen auf einer Platine zur Kommunikation mit nicht JTAG-fähigen Peripheriegeräten, z. B. DDR RAM- und Flash-Speicher.

Was ist ein JTAG-Verbindungstest?

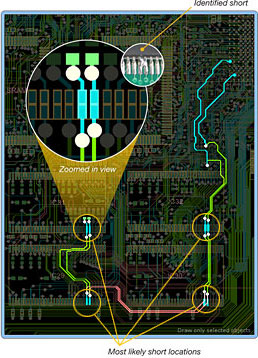

Mit einem JTAG-Verbindungstest wird geprüft, ob die Anschlüsse um die JTAG-fähigen Bausteine auf einer Leiterplatte den Designvorgaben entsprechen.

Wenn zwei JTAG-fähige Pins verbunden sein sollen, prüft der Test, ob ein Pin durch den anderen angesteuert werden kann. Wenn JTAG-fähige Pins nicht verbunden sein sollen, werden sie auf Kurzschlüsse geprüft. Dies geschieht durch Ansteuerung eines Pins und Überprüfung, dass diese Werte an den anderen Pins nicht gelesen werden können.

Fehlende Pull-Widerstände und Hängenbleiben können ebenfalls durch einen Verbindungstest entdeckt werden, ebenso wie Fehler unter Beteiligung von Logikbausteinen, deren Verhalten in einer Wahrheitswertetafel (Boolesche Verknüpfungstafel) beschrieben werden kann.

XJTAG erzeugt automatisch die Vektoren, die notwendig sind, um einen Verbindungstest auf der Grundlage der Verbindungsliste einer Leiterplatte und JTAG-Informationen über die JTAG-fähigen Bausteine durchführen zu können.

Was ist mit Bausteinen, die nicht JTAG-fähig sind?

Obwohl die wichtigsten Bausteine, wie Prozessoren und FPGAs, normalerweise JTAG-fähig sind, gibt es in jedem Design viele Bausteine, die es nicht sind. DDR, SDRAM, SRAM, Flash-Speicher, MDIO-gesteuerte Ethernet-PHYs, SPI- und I2C- Temperatursensoren, Echtzeituhren, ADUs und DAUs sind nur einige Beispiele für solche Bausteine.

Trotzdem bietet der Verbindungstest eine ausgezeichnete Erfassung von Kurzschlüssen auf den Verbindungen zwischen diesen nicht JTAG-fähigen und JTAG-fähigen Bausteinen. Allerdings kann er nicht auf Unterbrechungen bei JTAG-fähigen und nicht JTAG-fähigen Bausteinen prüfen.

Um diese Erfassung von Unterbrechungen hinzuzufügen, muss mit dem Peripheriebaustein über den Boundary-Scan am JTAG-fähigen Baustein kommuniziert werden. Wird eine Kommunikation bestätigt, kann kein Unterbrechungsfehler vorliegen. Diese Art der Prüfung kann sehr einfach sein, z. B. das Aufleuchten einer LED und Aufforderung eines Bedieners, zu überprüfen, dass sie aktiviert wurde. Sie kann aber auch komplexer sein, beispielsweise Schreiben von Daten in den Speicherblock eines RAM und Rücklesen dieser Daten.

Macht die Schaffung eines JTAG-Test-Systems viel Arbeit?

Mit der Verwendung der Bibliotheken für nicht JTAG-fähige Standardkomponenten, die von XJTAG bereitgestellt werden, können Sie ohne Code-Entwicklung sofort eine Reihe von Tests für Ihre Leiterplatte starten. Die Bibliotheksdateien enthalten Modelle für alle Arten von nicht JTAG-fähigen Bausteinen, angefangen bei einfachen Widerständen und Pufferspeichern bis hin zu komplexen Speicherbausteinen, wie DDR3. Da der Boundary-Scan die Ansteuerung der Pins auf JTAG-Bausteinen von ihrer Funktionalität trennt, kann dasselbe Modell verwendet werden, unabhängig davon, ob der JTAG-fähige Baustein eine Peripheriekomponente steuert oder nicht.

Die meisten Leiterplatten enthalten bereits JTAG-Sockel für die Programmierung oder Fehlersuche, so dass keine zusätzlichen Design-Anforderungen bestehen.

Wo finde ich Informationen über JTAG in meinen Bausteinen?

Um einen Boundary-Scan-Test durchführen zu können, sind einige Informationen über die Implementierung von JTAG auf den JTAG-fähigen Bausteinen der Leiterplatte notwendig. Diese Informationen befinden sich in BSDL-Dateien (BSDL = Boundary Scan Description Language) für diese Bausteine. Die BSDL-Dateien müssen vom Siliziumanbieter bereitgestellt werden, damit ein solcher Baustein mit dem Standard IEEE 1149.1 konform ist.

Wird der JTAG-Test nur in der Produktion verwendet?

Keineswegs. Einer der größten Vorteile des Boundary-Scan-Tests besteht darin, dass nur ein JTAG-Controller als einzige Testhardware erforderlich ist. Andere Produktionstesttechnologien, wie Flying Probe, automatische optische bzw. Röntgeninspektion oder Nadelbett erfordern allesamt spezielle Testausrüstungen, die am Ingenieursarbeitsplatz nicht verfügbar sind.

Die Anwendung des Boundary-Scan-Tests während der Leiterplattenentwicklung kann Unsicherheiten beseitigen. Hardware-Ingenieure können Prototyp-Leiterplatten vor dem Systemtest und sogar vor Fertigstellung der Firmware auf Fertigungsmängel prüfen. Testsysteme, die in dieser frühen Phase des Produktlebenszyklus entwickelt wurden, können einfach wiederverwendet und für die Produktion erweitert werden.

Warum sollte ich JTAG-Boundary-Scan für den Test meiner Leiterplatten verwenden?

Drei einfache Buchstaben – BGA

Eine zunehmende Anzahl von Bausteinen werden mit BGA-Gehäuse geliefert (BGA = Ball Grid Array). Jeder BGA-Baustein auf einer Leiterplatte sorgt für massive Einschränkungen der Prüfungen, die mit herkömmlichen Nadelbett- oder Flying-Probe-Maschinen durchgeführt werden können.

Durch die Nutzung einer einfachen Schnittstelle mit vier Pins ermöglicht der JTAG-Boundary-Scan die Ansteuerung und Überwachung der Signale an JTAG-fähigen Bausteinen ohne direkten physischen Zugang.

Drei weitere Buchstaben – NRE

Die NRE-Kosten (NRE = Non-Recurring Engineering) für den Bau von Prüfvorrichtungen können unerschwinglich hoch sein. In vielen Fällen kann der JTAG-Boundary-Scan eine solche Vorrichtung entbehrlich machen und in anderen Fällen kann die Vorrichtung stark vereinfacht werden, was zu beträchtlichen Kostensenkungen führt.

Kürzere Prüfzeiten

Bei Leiterplatten mit geringen Produktionsmengen war es schon immer schwierig, die Kosten für die Entwicklung von Prüfvorrichtungen zu rechtfertigen. In diesen Fällen ist die Flying-Probe-Prüfung eine Alternative. Allerdings sind die Prüfzykluszeiten bei dieser Technologie lang. Der JTAG-Boundary-Scan-Test bietet kurze Prüfzeiten ohne kostenintensive Vorrichtungen.

Niedrigere Testentwicklungskosten

Da unterschiedliche Prozessoren bzw. FPGAs mit Peripheriebausteinen in unterschiedlicher Weise interagieren, erfordert der herkömmliche Funktionstest eine teure kundenspezifische Entwicklung für jede Leiterplatte. Der JTAG-Boundary-Scan senkt solche Entwicklungskosten, da er eine vereinfachte Schnittstelle für die Ansteuerung der IO-Pins bietet, die mit Peripheriebausteinen zusammenspielen. Diese Standardschnittstelle, die bei allen JTAG-fähigen Bausteinen gleich ist, bedeutet, dass beim Aufbau von Testsystemen eine auswählbare Gruppe von Testmodellen verwendet und wiederverwendet werden kann.

Ein Tool für Prüfung und Programmierung

JTAG wird bereits oft für einen Schritt in der Produktion verwendet: die Programmierung. Durch die Verwendung von JTAG auch für den Boundary-Scan-Test kann die Anzahl der Schritte und Handhabungsvorgänge im Produktionsprozess reduziert werden.

Tests auf Produktionsebene am Ingenieursarbeitsplatz für Prototyp-Leiterplatten

Herkömmliche Prüftechnologien erfordern sehr große und teure Ausrüstungen. Für den JTAG-Boundary-Scan-Test ist nur ein einziges Testgerät erforderlich – ein JTAG-Controller. Der Controller XJLink2 von XJTAG hat die Größe einer PC-Maus.

Ausgezeichnete Fehlerdiagnose

Der JTAG-Boundary-Scan bietet anders als der Funktionstest sehr genaue Fehlerinformationen, die hilfreich für eine schnelle Reparatur sind. Außerdem bietet XJTAG die Möglichkeit der Anzeige sowohl der physischen Position eines Fehlers auf dem Leiterplattenlayout als auch des logischen Designs des Schaltkreisbereiches, in dem der Fehler auf dem Schema existiert.

Wiederherstellung „toter“ Leiterplatten, bei denen der Funktionstest nicht gelingt

JTAG-Boundary-Scan-Tests können an jeder Leiterplatte durchgeführt werden, die eine funktionierende JTAG-Schnittstelle hat. Herkömmliche Funktionstests können nicht durchgeführt werden, wenn die Leiterplatte nicht bootet. Einfache Fehler an wichtigen Peripheriebausteinen, wie RAM oder Clocks, würden mit JTAG entdeckt, aber die Funktionstests daran hindern, Diagnoseinformationen zu liefern.

Andere Quellen

Allgemeiner Leitfaden für JTAG

Erfahren Sie, was JTAG kann (In englischer Sprache)

Technischer Leitfaden für JTAG

Ein vereinfachter Blick auf die Umsetzung von JTAG

Design for Test (DFT)-Leitfaden

Vorschläge zur Verbesserung von Leiterplattentestbarkeit

JTAG-Testen mit XJTAG

XJTAG erweitert die Möglichkeiten von JTAG (In englischer Sprache)