Interview mit Stephen Love, CTO bei Xjtag

## Xjtag als Entwicklungsschnittstelle

Die für den PCB-Boundary-Scan wohlbekannte JTAG-Schnittstelle entwickelt sich zur Allzweckschnittstelle, von Verifikationsaufgaben, bis hin zur direkten Programmierung von Logikbausteinen, über das konventionelle Flashen hinaus. Wir sprachen mit Stephen Love, CTO bei Xjtag, darüber, welche Auswirkungen das für den Arbeitsfluss von konventionell gespaltenen Design- und Verfikationsingenieuren nimmt.

DESIGN&ELEKTRONIK: Herr

Love, das JTAG-Interface

kann zum Test, Prozessordebugging und zur direkten

Programmierung genutzt

werden. Weshalb wird es heutzutage

dennoch viel zu wenig eingesetzt?

Love: Nicht jeder ist mit JTAG vertraut

und nicht jeder, der schon mal Erfahrungen damit gemacht hat, weiß alles dar-

über. Wir wenden viel Zeit darauf, den Markt über die Vorteile von JTAG (Anm. d. Red.: einschließlich unentgeltlicher eintägiger Workshops) zu informieren, weil die meisten entweder nicht genug darüber wissen oder JTAG lediglich für einen Zweck verwenden, typischerweise für CPU-Debugging.

Wenn ein Projekt einen kurzen Entwicklungszyklus hat, kann die Testbarkeit leicht übersehen werden. Ingenieure haben oft nicht die Zeit, sich mit jeder einzelnen Lösungsmöglichkeit auseinander zu setzen. Deshalb bietet Xjtag unentgeltliche Testversion und Board-Setup, ohne jegliche Kaufverpflichtung. Auf diesem Weg können Ingenieure den JTAG-Test auf ihrer eigenen Leiterplatte ausprobieren und haben vom ersten Tag eine valide Lösung zur Verfügung.

D&E: Wie leistet JTAG hardwareunabhängige Abstraktion eines Systems? Weshalb sind 4/5-Signale dazu besonders effektiv? Benötige ich eine Firmware?

Love: JTAG wird aktiv angesteuert - benötigt jedoch keine Firmware. Die Pins von JTAG-Komponenten (Anm. d. Red.: Prozessoren, CPLDs, FPGAs etc.) werden vom

JTAG-Boundary-Scan-Testsystem gesteuert, das auf einem separaten PC läuft und die Pins werden als virtuelle Testpunkte auf der Leiterplatte verwendet. Der Gerätetyp oder die Kernarchitektur sind für das Testen irrelevant und Firmware ist unnötig, da das Testsystem über die Kontrolle verfügt. Der Vorteil einer 4/5-Pin-]TAG-Schnittstelle besteht darin, dass anstatt Dutzende oder Hunderte Testpunkte auf der Leiterplatte platzieren zu müssen, die Komponenten-Pins als virtuelle Testpunkte verwendet werden können und das allein ausgehend von dieser einzelnen 4/5-Pin-Verbindung. Da der Platz für Testpunkte oft begrenzt ist, kann dies ein sehr großer Vorteil sein. In Fällen, in denen Pins nicht direkt geprüft werden können (Anm. d. Red.: z. B. BGAs), ermöglicht JTAG Zugang zu Pins, auf die sonst nicht zugegriffen werden kann.

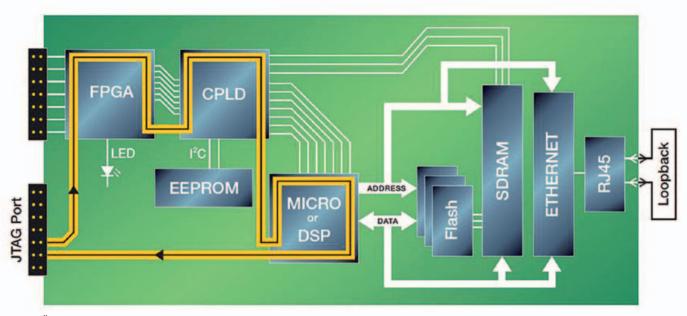

Da JTAG-Komponenten im Allgemeinen die zentralen Komponenten auf einer Leiterplatte sind, ermöglicht die Kontrolle der Anschlüsse dieser Vorrichtungen wiederum den Zugriff auf viele Nicht-JTAG-Komponenten auf der Leiterplatte, die so ebenfalls getestet und programmiert werden können.

Bild 2: Über JTAG-fähige Komponenten können prinzipiell alle weiteren verbundenen getestet werden (DDR-RAM, Flash, I2C-Komponenten, etc.).

# D&E: Bei Testmethoden stellt sich generell die Frage nach ihrer Aussagekräftigkeit. In welchen formalen Kriterien würden Sie die Aussagekraft von Tests auf Schaltungsniveau unterteilen?

Love: Ich denke, geeignet dazu sind die Fragen: Was bedeutet es, wenn meine Tests bestanden werden und wie steht das JTAG-Testen im Vergleich zu anderen Technologien? Verschiedene Technologien bieten unterschiedliche Maßnahmen, was immer ein Problem für den Nutzer darstellt. Ingenieure sind im Allgemeinen mit Nagelbrett- und Flying-Probe-ICT-Tests vertraut, JTAG-Tests sind diesen Technologien im Wesentlichen ähnlich. JTAG-Tests werden daher wahrscheinlich am ähnlichsten mit ICT-Tests hinsichtlich ihrer Fähigkeiten und ihres Zugriffs verstanden - obwohl JTAG-Tests mit Strom versorgt werden und somit die Funktionalität der Leiterplatte nutzen können, um Tests über einfache Kurztests hinaus zu erweitern.

#### Testbarkeit sollte fester Bestandteil der Designkriterien sein und Testmöglichkeiten müssen von Anfang an berücksichtigt werden!

Die Verwendung der JTAG-Pins als virtuelle Testpunkte reduziert den Bedarf an physikalischen Testpunkten erheblich, was den Testzugang zu kompakten Leiterplatten verbessert und auch die Kosten von Testvorrichtungen verringert. Obwohl JTAG die Korrektheit digitaler Komponenten und das Vorhandensein vieler Widerstände prüfen kann, appliziert es jedoch nicht direkt analoge Messungen, beispielsweise von Widerstandswerten. Wie beim ICT-Test gibt es beim JTAG-Test keinerlei Informationen über Lötqualität oder Komponentenausrichtung. Viele Unternehmen entscheiden sich daher, die Stärken von

JTAG mit anderen Testvorrichtungen wie Flying Probe, Nagelbett-ICT-Maschinen, AOI, Funktionstestern und verschiedenen anderen Anbietern zu kombinieren, um die auf einer Leiterplatte durchgeführten Tests zu optimieren. Jede Testmethode hat Stärken und Schwächen. Daher sollten idealerweise komplementäre Methoden verwendet werden, die zu Anwendung und Budget passen.

Es soll an dieser Stelle jedoch noch einmal darauf hingewiesen werden, dass einer der Vorteile von JTAG darin liegt, dass seine Anwendung nicht auf das Werk beschränkt ist die erforderliche Ausrüstung ist kompakt und die Kosten sind gering genug, dass Produkte wie XJDeveloper, die Testentwicklungsumgebung von Xjtag, für den Einsatz im Büro, Labor oder auch auf der Fertigungsstrecke in Betracht gezogen werden können.

D&E: JTAG ragt im Laboreinsatz durch einfachen Zugang heraus? Hat man nicht generell immer ein Problem in Platinenkontaktierung? Wie anfällig ist die Testperformanz für steigende Integrationsdichte? Welche Fehler kann man in der Kontaktierung begehen?

Love: Sonden bedienen sich der gleichen Technologie wie Nagelbett-Tester und die Einschränkungen, die sie mit sich bringen, sind bekannt. Wenn jedoch die JTAG-Signale angeschlossen werden, bedarf es nur des Anschlusses einer kleinen Anzahl von Sonden. Die Reduzierung der Testpunkte durch die Verwendung von JTAG-Tests macht Testvorrichtungen kosteneffizient, einfach und somit zuverlässig. Viele Kunden verwenden keine Sonden, sie verwen-

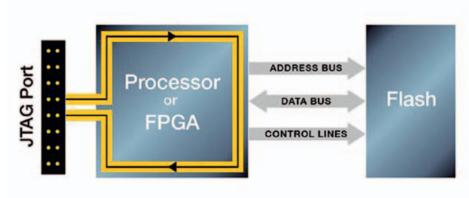

Bild 1: Bei der direkten Programmierung wird über JTAG auf eine verarbeitende Komponente zugegriffen, die dann den Speicher beschreibt.

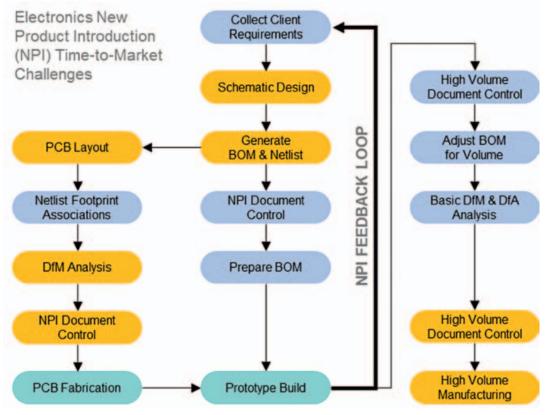

Bild 3: Anforderungen bei der Neuentwicklung von Produkten.

den jedoch einen Connector — egal, ob es sich um einen Tag-Connect-Connector oder einen Box-Header handelt.

Es gibt Komponenten, bei denen selbst für diese geringe Anzahl von Verbindungen der Platz schwer zu finden ist. Aus diesem Grund wurden 2-Signal-Versionen von JTAG entwickelt und man wird in den nächsten Jahren weitere Komponenten sehen, die diesen Markteintritt unterstützen. Im Allgemeinen kann Platz für fünf Signale gefunden werden, die an das Board angeschlossen werden, weil sie Dutzende oder gar Hunderte von Testpunkten an anderer Stelle auf dem Board einsparen.

Was die Erhöhung der Komponentendichte anbelangt – JTAG wurde speziell für diesen

Fall entwickelt und bewältigt die Problematik besser als jede der konkurrierenden Testtechnologien. Die Testzeiten steigen sobald ein Board komplexer wird, aber sie bleiben kurz und steigen im Allgemeinen deutlich langsamer als die Größe der Leiterplatte.

D&E: Wie früh sollte man die Testbarkeit im Entwicklungsfluss neuer Produkte berücksichtigen? Kann man diese auf formale Kriterien reduzieren? Gibt es einen Konflikt mit Time-to-Market?

Love: Testbarkeit sollte fester Bestandteil der Designkriterien sein und Testmöglichkeiten müssen von Anfang an berücksichtigt werden! Die Empfehlung von Xjtag lautet, dass Tests neben anderen Designregeln als gleichwertige Anforderung eingestuft werden sollten. Bei Designregeln sollte es nicht ausschliesslich darum gehen, die Produktion zuverlässig zu machen (Anm. d. Red.: Abstände, Pad-Größen etc.), sie können auch dazu dienen, das Design testbar zu machen. Diese Überlegungen sollten die Komponentenauswahl, das Schaltplandesign, das Platinenlayout usw. in jeder Phase beeinflussen. Wenn nicht vorher überlegt wird, wie eine Platine getestet werden kann, ist ein Projekt schon früh zum Scheitern verurteilt.

Was die Markteinführungszeit anbelangt: Das Wissen, dass ein Board testbar ist, verbessert die Vorhersagbarkeit und verringert auch die Wahrscheinlichkeit der Verspätung eines Projekt aufgrund langer

Anzeige

Debugging-Zeiten, unnötiger Überarbeitung von Boards und möglicherweise der Notwendigkeit eines Respins zur Verbesserung der Testbarkeit für die Produktion. D&E: Typischerweise ist Elektronikentwicklung in die Lager Design und Verifikation gespalten. Automatisiert JTAG die Verifikation derart, dass ein Designer bereits in der Entwicklung Verifikationsinformationen erhält? Ich dachte immer, Verifikation fordert ein kreatives Element, da es quasi darum geht das Design auszuhebeln?

Love: Xjtag wurde von Designingenieuren entwickelt, die feststellten, dass existierende Tools aus dem Bereich der Fertigung stammten und sehr teuer, extrem komplex und restriktiv lizenziert waren. Oftmals erforderten sie zudem Fachschulungen.

Die Einführung von Xjtag in den Markt und die damit einhergehende Kosteneffizienz versetzte den Markt in Aufruhr. Ingenieure wurden von der bis dato üblichen Komplexität von JTAG befreit, indem ihnen ein einfach zu bedienendes Tool zur Verfügung gestellt wurde, das Nicht-JTAG-Komponenten mit wiederverwendbaren Vorlagen besser testen konnte. Auch die Einführung flexibler Lizenzierungen war neuartig.

Aufgrund seiner Wurzeln hat Xjtag immer versucht, sowohl Designingenieure als auch Prüfer anzusprechen.

In Wirklichkeit haben Designingenieure oft auch die Verpflichtung zur Verifizierung (auch wenn sie dies nicht so sehen), weil sie in der Regel für die Leiterplattenerstellung ihrer eigenen Designs verantwortlich sind. JTAG kann in diesem Stadium eines Projekts sehr nützlich sein, weil es nicht von der Firmware abhängig ist, oder gar zu einem früheren Zeitpunkt, weil schon allein durch die Einrichtung eines JTAG-Projekts eventuelle Designprobleme hervortreten können.

#### In Wirklichkeit haben Designingenieure oft auch die Verpflichtung zur Verifizierung.

Es besteht auch die Möglichkeit, der Entwicklungsumgebung spezifische Verifikationstools hinzuzufügen - das beste Beispiel sind Xjtags DFT-Assistant-Design-Validierungs-Plugins für alle wichtigen EDA-Tools. Diese werden kostenlos zur Verfügung gestellt und entstanden, weil Xjtag feststellte, dass obwohl JTAG in Datenblättern erwähnt wird, die Tools, die die JTAG-Fähigkeit nut-

zen, erst nach Fertigstellung der ersten Hardware relevant werden. Um in dieser Phase noch Probleme mit JTAG zu erkennen ist es zu spät: kostspielige Re-Spins oder das Erstellen umständlicher Funktionstests sind nicht mehr vermeidbar.

D&E: Wie sieht ein funktionaler Test mit JTAG aus? Wie werden die Komponenten dabei mit Daten beschrieben und evaluiert? Wird funktionale Abdeckung erreicht? Welche Fehler sind prinzipiell damit auffindbar?

Love: Es muss an dieser Stelle sehr auf die Terminologie geachtet werden. JTAG-Tests sind *normalerweise* keine Funktionstests. Stattdessen verwenden sie die Funktionalität von Komponenten auf einer Leiterplatte, um die Verbindungen auf dieser zu überprüfen. In der Regel wird also etwas an den Eingängen einer Komponente vorgenommen und dann überprüft, ob eine erwartete Antwort von den Geräteausgängen zurückkommt. Das kann so simpel sein wie das Empfangen eines ACK von der korrekten Adresse für eine I2C-Komponente oder komplexer, wie das Überprüfen, ob Speicher geschrieben und dann zurückgelesen werden kann. Der Test zielt jedoch nicht darauf ab, die vollständige Funktion solcher Komponenten zu überprüfen, sondern soweit sicherzustellen, dass die richtige Komponente installiert und korrekt angeschlossen ist.

JTAG-Boundary-Scan-Tests sind bekannt dafür, Kurzschluss- und Leerlauffehler auf einer Leiterplatte zu finden. Aber sie erkennen auch andere Fehler, wie zum Beispiel einen falschen IC. Xjtags Herangehensweise ist es JTAG-Tests aus drei Hauptdatenquellen zu generieren, die die getestete Platine beschreiben: BSDL-Dateien, die den JTAG-Gerätebetrieb beschreiben, Netzliste, beschreibt die Leiterplatte selbst, und Komponentenmodelle – beschreiben, wie Nicht-JTAG-Komponenten getestet werden können. Xjtag verfügt über eine Bibliothek von Modellen für Tausende von Komponenten, die im Softwarepaket enthalten ist.

D&E: Über die JTAG-Schnittstelle könnte ich direkt eine arithmetische Komponente auf dem Board programmieren, die dann auf das Flash schreibt. Muss ich dafür Assembler beherrschen? Ist diese direkte Programmierung schneller gegenüber konventionellen Flashmethoden. Wie anfällig ist dieser Vorgang für R/W-Fehler?

Love: Dies ist ein übliches Mittel zum Programmieren - es ist schneller als die

Stephen Love, CTO bei Xitag

Verwendung von JTAG auf herkömmliche Weise, da es nicht darauf beschränkt ist, die JTAG-Kette für jeden Pin-Übergangsschritt zu scannen. Wenn ein solches Programm selbst in Assembler oder C geschrieben werden kann, ist das fantastisch. Wenn dies nicht der Fall sein sollte ist es möglich, dass der JTAG-Hersteller dies bereits getan hat, was viel Arbeit erspart. Mit einer solchen Methode ist es viel einfacher die Nutzung vorprogrammierter Flash-Komponenten zum Produktionszeitpunkt zu vermeiden.

In Bezug auf Fehler hängt die Fehlerrate direkt von der Signalintegrität des Datenpfads ab, der auf der Leiterplatte verwendet wird. Die Erhöhung der Programmiergeschwindigkeit macht es zudem praktikabler, die zu programmierenden Daten zu verifizieren. Um dies zu erreichen kann die Software auf der Platine beispielsweise eine Prüfsumme berechnen.

D&E: Können Sie ein paar Beispiele für diese direkte Programmmierung geben? Love: Bei Xjtag wird die beschleunigte Programmierung in zwei Kategorien eingeteilt - es gibt ein Produkt namens XJDirect, das ein Programm in eine CPU lädt und ausführt - damit können die Daten über eine komfortable Schnittstelle in die CPU geladen und dann in Flash programmiert werden.

Das andere Produkt zur beschleunigten Programmierung heißt XJFlash und funktioniert, indem ein Image in ein FPGA geladen wird, wodurch das FPGA zum Programmierer wird. In diesem Fall werden die zu programmierenden Daten über die JTAG-Signale an das FPGA gestreamt, welches es wiederum in den Flash schreibt. Beide Methoden führen zu einer erheblichen Verbesserung der Programmiergeschwindigkeit. Es ist üblich, dass eine beschleunigte Programmierung durch die Schreibgeschwindigkeit der Flash-Vorrichtung und nicht durch die Datenraten in der Schaltung begrenzt wird. Diese Leis-

tung bedeutet, dass Flash im Allgemeinen in der Produktionslinie programmiert werden kann, ohne dass Vorprogrammierungen benötigt werden.

**D&E:** Wie gewährleistet man Signalintegrität für die JTAG-Verbindung? Können Sie ein paar Tipps für das Design der JTAG-Verbindung geben? Inwiefern leistet das ihre Software? Love: Die Tatsache, dass das JTAG-Testen live ist und Signale mit relativ hoher Geschwindigkeit verwendet, stellt einige grundlegende Anforderungen an das Leiterplattenlayout und an die Verkabelung, die für die Prüfung der Leiterplatte verwendet wird. Diese korrekt zu implementieren, bevor die Leiterplatten die Produktion gegeben wird, ist dementsprechend sehr wichtig. Der beste Weg um sicherzustellen, dass dies korrekt geschehen ist, ist ein Tool wie den DFT-Assistant von Xjtag zu verwenden, um das Design schon in der schematischen Phase des Designs zu validieren.

Der Xjtag DFT Assistant ist ein kostenloses Tool, das in Altium-Designer, OrCAD, Mentor Graphics PADS/Xpedition und Zuken CR-8000 enthalten ist. Durch die Validierung der korrekten Implementierung von Boundary-Scan-Ketten und die Einhaltung der optimalen Vorgehensweisen von Design-for-Test werden potenzielle Probleme frühzeitig im Entwurfszyklus erkannt. Der DFT Assistant umfasst den Xjtag Chain Checker und den Xjtag Access Viewer.

### ■ JTAG-Boundary-Scan-Tests sind bekannt dafür, Kurzschluss- und Leerlauffehler auf einer Leiterplatte zu finden.

Der Xjtag Chain Checker analysiert die Netzliste und findet eine routbare Scan-Kette. Er bietet auch eine einzigartige DFT-Funktion: Die Überprüfung, ob die JTAG-Signale korrekt abgeschlossen sind. Der Xjtag Chain Checker identifiziert potentielle Fehler und Warnungen, die in JTAG-Ketten gefunden werden, zum Beispiel: Verbindungsfehler, wenn eines der JTAG-Test-Access-Point-Signale, TAP, an die falschen Pins eines JTAG-kompatiblen ICs angeschlossen ist; Beendigungswarnungen, wenn eines der TAP-Signale nicht wie empfohlen beendet wird; Compliance-Pin-Fehler, wenn sie fälschlich high oder low gezogen werden oder erdfrei bleiben. Der Xjtag DFT Assistant identifiziert auch den Umfang des JTAG-Zugriffs auf einem gesamten Schaltplan. Dieser wird mit dem Xjtag Access Viewer auf den Schaltplan überlagert, so dass Designingenieure ihre Testabdeckung bereits in einem frühen Stadium des Designs nachvollziehen können.

Durch die Visualisierung des Ausmaßes der Testabdeckung können die Ingenieure sehen, wie sich Änderungen des Designs auf die Testabdeckung auswirken, da sie zunehmen, wenn zusätzliche Netze auf der Leiterplatte für Boundary-Scan zugänglich gemacht werden.

Weitere Tipps für gute Leistung sind: Minimierung potenzieller Überlagerungen, indem aktive Signale mit GND-Pins der JTAG-Anschlussverkabelung verschachtelt werden; Vermeiden Sie TDO neben TCK. (Anm. d. Red.: TDO-Übergänge treten an den abfallenden Flanken von TCK auf; daher können Überlagerungen von TDO Störungen in TCK verursachen und die Daten korrumpieren). Stellen Sie gute Erdverbindungen zwischen dem zu testenden Board und dem JTAG-Controller her.

Für weitere Ideen stellt Xjtag unentgeltlich Design-for-Test-Richtlinien zur Verfügung, die auf der Xjtag-Website verfügbar sind. D&E: Wie verbessert eine DFT die funktionale Abdeckung eines JTAG-Tests? Love: Wichtig ist, dass bei der Entwicklung des Designs weiter analysiert wird - die Analyse der Testabdeckung ist ein wesentlicher Bestandteil des Schaltungsdesigns. Nur wenn der Umfang der Tests überprüft wird kann nachvollzogen werden, an welcher Stelle die Testabdeckung verbessert werden muss. Die Analyse wird auch Bereiche des Boards identifizieren, die zu besagtem Zeitpunkt nicht mit JTAG getestet werden können oder bei denen bereits eine geringfügige Designänderung die Testabdeckung erheblich verbessern würde. Es können auch Bereiche identifiziert werden, in denen Testpunkte entfernt werden können, wodurch Platz auf der Leiterplatte eingespart und Prüfvorrichtungen vereinfacht werden können.

JTAG-Tests sind in der Regel kostengünstiger zu erstellen als Funktionstests, aber der Testzugang ist final, wenn das Hardwaredesign abgeschlossen ist. Daher ist es extrem wichtig diese Tatsache früh zu berücksichtigen, bevor es zu spät ist.

Wenn ein Projekt mit Tools wie dem Xjtag DFT Assistant in der Entwurfsphase kurz vor der Fertigstellung steht und ein vollständiges JTAG-Setup für das Prototyp-Debugging durchgeführt wird, ist dies sowohl für den Schaltungsentwickler in Bezug auf die

Board-Bringup-Zeit als auch für den Hersteller in Bezug auf die Produktqualität von Vorteil. Herr Love, vielen Dank für das Gespräch und Ihre Zeit!

Das Interview führte Dr. Constantin Tomaras.