# Cornerstone of production test

Contract manufacturers striving to meet test coverage and cycle-time challenges are increasingly using the latest boundary scan equipment to co-ordinate multiple techniques including functional test and built-in self test

roduction test strategies for complex products are changing dramatically to respond to demands for time and cost savings, in addition to technical challenges such as diminishing access for traditional test probes. The latest advances in boundary scan testing implement sophisticated virtual probes, and provide a flexible platform for composite test routines to overcome modern commercial and technical pressures.

## Changes in production test

Traditionally, in-circuit test (ICT) has been the mainstay of the production test engineer's arsenal. However, diminishing test access is a serious challenge to this approach. Contributing factors include the growing use of CSP and BGA packages, which prevent probes from directly contacting the I/Os of devices such as SoCs, memories, microcontrollers and FPGAs. Dense double-sided and multi-layer boards also prevent access to inter-IC signals. Fabricating dedicated test points has ceased to be an option in most cases, due to factors such as limited real estate and the negative effects on signal integrity at high speeds.

To address these issues, as well as streamlining test development and saving costs, hybrid test strategies are emerging that combine more modern techniques such as boundary scan, custom functional tests and built-in self test. In this way, manufacturers are able to optimise the test strategy for a given board to meet testability goals, satisfy specific test requirements, and achieve an acceptable cycle time.

In many respects, boundary scan is ideally positioned to form the central element of such a hybrid strategy. Since low test coverage due to lack of probe access impacts on a project from the development and debugging stages onwards, board designers are increasingly implementing boundary scan infrastructure into new boards to solve these issues. With the latest tools and test techniques, test coverage greater than 90 per cent is possible using boundary scan alone. Combining boundary scan with other test

September/October 2008 Electronics Assembly

Tim Murrell, PartnerTech King's Lynn with the XJTAG system

techniques allows production routines to achieve close to 100 per cent coverage with minimal probing of the board

# Extending test coverage

Today's boundary scan tools maximise opportunities to use the boundary scan chain and connected JTAG devices to test non-JTAG components on the board. Custom tests can be written and incorporated easily into the boundary scan routine, or downloaded from vendor websites as pre-written tests for standard components such as Ethernet ports or video interfaces. The test equipment automatically calculates how to use the boundary scan infrastructure to carry out the test.

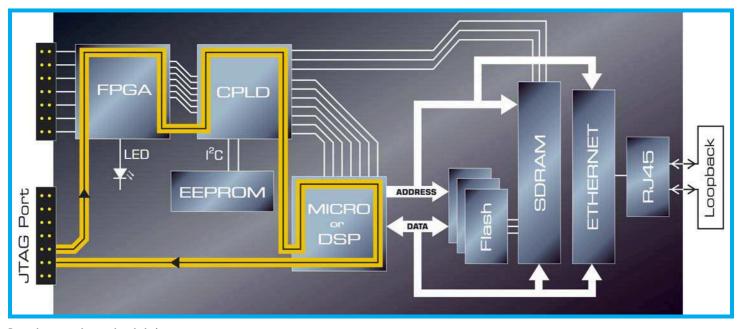

I/O expansion modules extend the testability of non-JTAG devices still further. Connecting the module to the board via the JTAG Test Access Port (TAP) allows signals to be brought out to a number of bidirectional digital I/Os and analogue I/Os on the module, which can be configured and monitored from within the boundary scan test environment. In this way, engineers can use boundary scan to test large numbers of signals all the way through to external connectors. Onboard ADCs also enable testing of power rail levels. Other innovations that increase test coverage and reduce test development time include prewritten code to manipulate industry-standard interconnects such as an I2C or SPI bus, which greatly increases communication with non-JTAG devices from within the boundary scan environment.

Some tools, such as the XJTAG boundary scan development system, incorporate a high-level testprogramming language, which allows test engineers to compile detailed tests without having to understand how boundary scan works. Because the tests are written with reference to the device's properties alone, for example by specifying the pin levels required to run the test and any pin states expected as a result tests can be re-used in subsequent projects without any additional work. The test equipment automatically calculates the test patterns that will achieve the required inputs.

# **Central strategy**

As an example of how boundary scan is playing a key role in the evolution of production test strategies, PartnerTech, one of Europe's leading contract manufacturing companies with 13 manufacturing centres and some 1,700 employees at sites in Sweden, Norway, Finland, Poland, UK,

United States and China, is using the XJTAG boundary scan system at its King's Lynn facility, to co-ordinate multiple test technologies.

The XJTAG boundary scan system is designed to speed up debug, test and programming of electronic printed circuits boards and systems throughout the product lifecycle. And it provides a convenient way to control a hybrid test strategy, for example to test systems containing a mixture of analogue and digital signals, as it includes specific software which allows calling of external test applications and thirdparty programming tools, and displays all the results in a GUI.

Tim Murrell, senior electronics engineer at PartnerTech's King's Lynn facility, explained: "On one board we have a DSP with a combination of digital and analogue pins. We use XJTAG to exercise the digital pins directly, and we are also using it to coordinate functional tests and built-in tests for the remainder of the device." This capability can save considerable time and expense compared to writing a custom executive and GUI using a functional test development tool, for example, and provides a convenient turnkey solution where a straightforward go/no-go indication is required.

To boost test coverage within the boundary scan environment, PartnerTech is able to build its own custom I/O expander modules using inhouse dry PCB fabrication facilities. Implemented using a JTAG-compatible CPLD and designed to be inserted in the scan chain, these boards operate in a similar way to the off-the-shelf I/O modules. "The expander module becomes part of the scan chain and increases access to I/Os on the unit under test," added Tim Murrell. "We can carry out loopback-type tests, for example, within XJTAG, which saves us building loopback connectors and also provides better diagnostics to help locate faults. Benefits include faster test cycles and higher production yield."

PartnerTech is taking advantage of a number of boundary scan utilities including XJRunner, a run-time-only environment that significantly reduces the cost of ownership for multiple test seats. Operators benefit from full testing capabilities, including interconnect testing, in-system programming and non-JTAG device testing. The run-time environment also supports a variety of serial number systems, as well as configurable logging to assist auditing and quality assurance.

## Cost and time savings

Modern manufacturers seeking to save time in test development can take advantage of graphical tools designed to speed up the preparation of basic test descriptions. Getting the basic aspects of a boundary scan test routine working can usually take around a day. This is considerably quicker than is normally possible with traditional technologies such as ICT, but the latest graphical interfaces such as XJTAG's XJDeveloper achieve extra savings by allowing drag-and-drop functions and automating processes such as scanchain detection.

Tim Murrell explained: "These utilities make assembling infrastructure tests and basic device tests particularly easy. We can have a basic boundary scan test up and running in as little as an hour, and compiling tests will become even quicker in future as we grow our library of reusable device-centric scripts."

Even if a set of boundary scan tests has not been compiled for a given board, ad hoc testing can still be performed, for example to toggle signals and quickly confirm basic operation. When the board is

### XJTAG's XJDeveloper GUI automates the scan-chain detection

connected, real-time circuit visualisation and debugging utilities automatically identify the scan chain, locate the correct BSDL files, and provide a graphical view of JTAG chains and pin states. With the ability to toggle physically inaccessible pins, trace signals, locate shorts or opens, and also program devices with SVF and STAPL files, this capability helps contract manufacturers improve yields by quickly and easily providing detailed diagnostics for any board incorporating boundary scan infrastructure.

### Platform for growth

By providing a platform capable of supporting an entire test strategy comprising multiple test technologies, and offering numerous capabilities and features to trim time and cost from production test, boundary scan is profoundly changing the way modern contract manufacturers build their test strategies. At PartnerTech in King's Lynn, XJTAG boundary scan has also played a key role in helping the company grow its test engineering services as OEMs seek to outsource this activity to gain additional cost savings. Whereas five years ago the company was responsible for test engineering on around 50 per cent of its builds, this has risen to 70 per cent today.

Tim added: "We have invested in a number of powerful tools to support this growth, and XJTAG has played a significant role in enabling us to satisfy customers' needs quickly and cost effectively. This is yet another way by which modern boundary scan technology provides today's contract manufacturers with a test philosophy, strategy and technical platform to meet future demands for low-cost, high-tech electronic products."

### www.xjtag.com www.partnertech.com

Boundary-scan bus to local chains