# XJTAG<sup>®</sup> DFT Assistant for

# Orcade Cade Colutions Capture

## Installation and User Guide

Version 2.1

## Table of Contents

#### SECTION

#### PAGE

| 1. Introduction                             |

|---------------------------------------------|

| 2. Installation                             |

| 3. Quick Start Guide                        |

| 4. User Guide                               |

| 4.1. Background4                            |

| 4.2. Setup Overview4                        |

| 4.3. Workflow                               |

| 4.3.1. Generating the netlist6              |

| 4.3.2. Categorising JTAG devices8           |

| 4.3.3. Defining JTAG Chain(s)8              |

| 4.3.4. Categorising passive devices9        |

| 4.3.5. Manually creating a passive device11 |

| 4.4. Check JTAG Chain12                     |

| 4.5. XJTAG Access Viewer14                  |

| 5. Export XJDeveloper Project               |

| 5.1. Boundary Scan test development16       |

| 5.2. Migrating a project to XJDeveloper17   |

| 6. Troubleshooting                          |

| 7. Further reading                          |

| About XJTAG                                 |

### 1. Introduction

**XJTAG DFT Assistant for OrCAD Capture** is a *Software Plugin* for the **OrCAD Capture** platform, developed by XJTAG, a leader in JTAG/Boundary Scan technology. The plugin provides added functionality to the platform in the form of running Design For Test (DFT) checks on boundary scan chains in a schematic diagram. These checks ensure the scan chain is correctly connected to each JTAG-enabled device in the design, as well as checking that each signal in the chain has been correctly terminated.

The plugin is made available free of charge.

Please note, this plugin requires OrCAD Capture 17.2 or higher. Visit <u>www.orcad.com/resources/orcad-downloads</u>

### 2. Installation

The plugin can be installed via a stand-alone installer available from **XJTAG.com** or **OrCAD.com**.

Before installing the plugin, OrCAD Capture must already be installed, as well as **Microsoft .NET Framework 4.7.1** or higher.

Download and run the XJTAG DFT Assistant for OrCAD Capture.msi installer file.

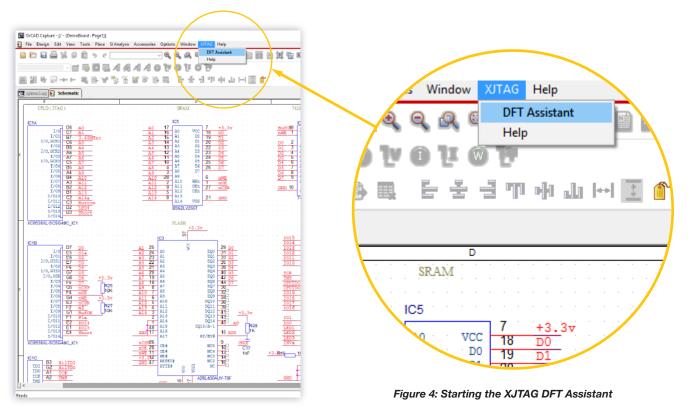

Once the plugin has been installed, an XJTAG drop down menu will be added to the *Menu Bar* in **OrCAD Capture**. The plugin can be launched via this menu.

Updates for the plugin will be made available periodically via **XJTAG.com** or **OrCAD.com**. Emails will be sent to all registered users to inform them when updates have been released.

## 3. Quick Start Guide

- 1 Install XJTAG DFT Assistant for OrCAD Capture (See Section 2)

- 2 Open an OrCAD Capture design, or start a new design

- 3 Open the XJTAG DFT Assistant from the Menu Bar

- 4 Assign BSDL files to all JTAG-enabled devices in the design (See Section 4.3.2)

- 5 Define the scan chains and their TDI and TDO pins (up to four scan chains) (See Section 4.3.3)

- 6 Categorise any passive devices in the chain(s) (See Sections 4.3.4 & 4.3.5)

- 7 Run the XJTAG Chain Checker (See Section 4.4)

- 8 Run the **XJTAG Access Viewer** (See Section 4.5)

## 4. User Guide

## 4.1. Background

Boundary scan, as defined by the IEEE 1149.x family of standards, is a technology which enables a JTAG-enabled Integrated Circuit (IC) to relinquish control of its pins to an external agent for test purposes. The logic required to do this is included in the IC at each JTAG-enabled pin, known as a boundary scan 'cell'. These cells are connected in series within the IC and accessed externally through a 4- or 5-pin port known as a Test Access Port, or TAP.

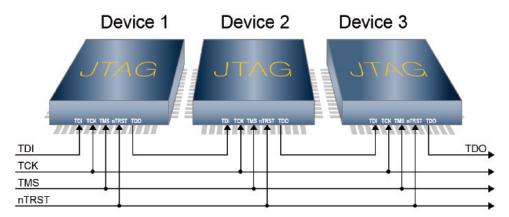

Figure 2: A boundary scan chain connecting three ICs

The TAP on each JTAG-enabled IC can be connected serially creating what is referred to as a boundary scan chain (*see Figure 2*). As each IC is a link in this chain, it is imperative that the chain's integrity is maintained through its entirety; from where it enters the board, to where it leaves. Typically this would be on two pins of the same connector.

The **XJTAG DFT Assistant for OrCAD Capture** software plugin provides a level of automation in checking that one (or many) scan chain(s) on a PCB are connected and terminated correctly. Crucially, these tests are carried out at the schematic capture stage, thereby identifying errors early in the design cycle and helping to avoid costly PCB respins.

## 4.2. Setup Overview

Because the software plugin is fully integrated into OrCAD Capture, most of the information needed to conduct a DFT check of a boundary scan chain, such as a netlist and BOM, can be accessed within the platform automatically. However, it is also necessary to provide some additional information that would not normally form part of an OrCAD Capture design. Specifically, a Boundary Scan Description Language (BSDL) file must be provided for each JTAG-enabled device in the design.

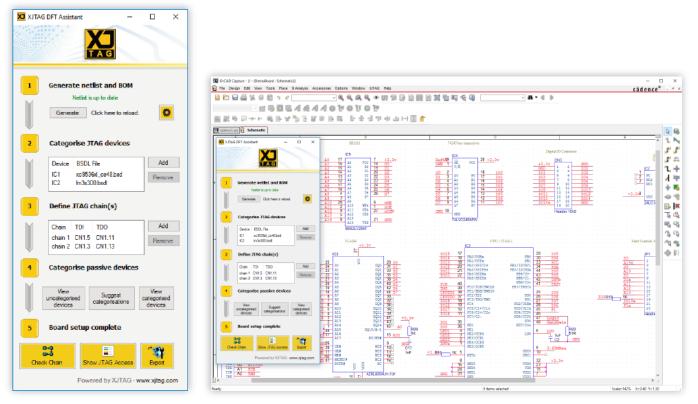

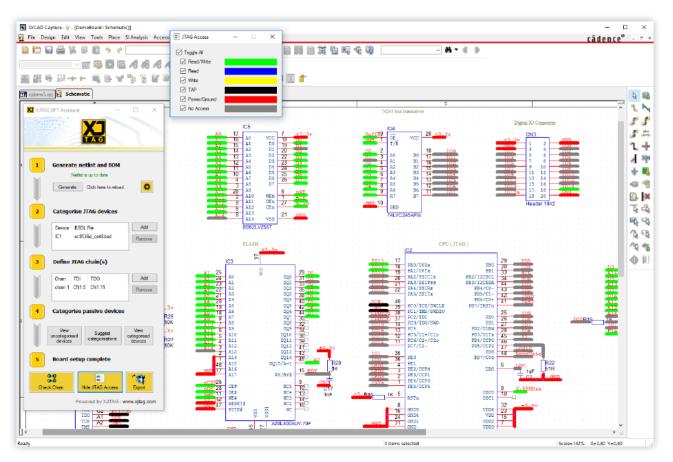

Figure 3: The DFT Assistant User Interface

In order to comply with the IEEE standard, it is a requirement for the IC manufacturer to supply a BSDL file for each JTAG-enabled device. Sourcing BSDL files is, therefore, not difficult but it is recommended they be obtained direct from the manufacturer's website in order to guarantee they are the latest versions.

BSDL files can be assigned to ICs using the **XJTAG DFT Assistant for OrCAD Capture** interface, which is in a separate window but will always stay visible above the OrCAD Capture main window (see *Figure 3*).

Once a BSDL file is imported and associated with an IC it is stored as part of the OrCAD Capture design, so the process does not need to be repeated.

Other non-JTAG devices that may propagate boundary scan access or form a part of the JTAG chain include standard logic and passive devices. The **XJTAG DFT Assistant for OrCAD Capture** will help identify any such devices in the schematic and allow the designer to categorise them. In addition, pressing the *Suggest Categorisations* button will attempt to auto-categorise any commonly seen components such as series resistors and pull resistors. Any devices not categorised can be assigned later if the design is exported and opened in **XJDeveloper** (see Section 5.0 for more details). All categorisation information will also be stored as part of the design.

### 4.3. Workflow

The **XJTAG DFT Assistant for OrCAD Capture** panel opens as a new window after selecting *DFT Assistant* from the *XJTAG Menu Bar*. If the assistant window is already open, it will give the window focus *(see Figure 4)*.

There are four stages to performing a board setup:

- Generate the netlist

- Categorise JTAG devices

- Assign JTAG TDI and TDO pins, and

- Categorise passive devices.

Once the netlist has been generated, the remaining actions can be carried out in any order and will be discussed in more detail below. After board setup is complete there are three options available to the user at the bottom of the Assistant panel: Check the JTAG Chain, Show/Hide JTAG Access, or export XJDeveloper project.

#### 4.3.1. Generating the netlist

When the Assistant panel is opened for the first time, most of the UI will be disabled until a netlist is generated by clicking on the Generate button towards the top of the panel (see Figure 5).

It is a requirement to generate netlist and BOM information for the current OrCAD Capture design before any DFT analysis can be carried out. If the design is changed while the Assistant is open, the netlist should be updated by clicking again on the Generate button. This will carry out a netlist update in the background and a progress bar will be displayed while this happens.

Figure 5: Generating the netlist automatically using XJTAG's internal netlist builder

If an error is reported while automatically generating the netlist, it is possible to use a manually created netlist instead. To do this, select the project in OrCAD Capture and click the *Tools > Create Netlist...* menu item. XJTAG supports many netlist formats but the recommended format is **RINF** (see Figure 6). Make sure the option *Output part attributes* is also ticked.

| Create Netlist                                                                                                                         |                                                                                                       | ×      |

|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------|

| PCB EDIF 2 0 0 INF                                                                                                                     | PSpice SPICE Verilog VHDL Other                                                                       |        |

| Part Value<br>Combined property str<br>{Value}                                                                                         | PCB Footprint<br>Combined property string:<br>{PCB Footprint}                                         |        |

| Formatters:<br>orRinf64.dll<br>orPcbii64.dll<br>orPdmp64<br>orPldmet64.dll<br>orprote1264<br>orracalred6<br>orRinf64.dll<br>viriardif6 | Options<br>Fag single-pin nets<br>Use metric units<br>Output part attributes<br>Output net attributes |        |

| Version: 17.4.0 Aug 8<br>Netlist File 1: View                                                                                          |                                                                                                       | Browse |

|                                                                                                                                        |                                                                                                       | Browse |

| Netlist File 2: View                                                                                                                   | BOARD\DEMD BOARD V4.CMP                                                                               | Browse |

| Use Config File<br>Netist Config File:                                                                                                 |                                                                                                       | Browse |

|                                                                                                                                        | OK                                                                                                    | Help   |

Figure 6: Generating the netlist manually

Back in **XJTAG DFT Assistant for OrCAD Capture**, click the Settings button and browse to the created netlist (see Figure 7).

| Netlist Settings                                               | × |

|----------------------------------------------------------------|---|

| Netlist Builder O Internal XJTAG netlist builder [Recommended] |   |

| Copy netlist file Browse                                       |   |

| C:\CADENCE_PROJ\MAIN TESTING\JTAGDEMODESIGN\XJDEMO3.NET        |   |

| OK Cancel                                                      |   |

Figure 7: Using the manually created netlist file

Click the *Generate* button again to use the created netlist.

#### 4.3.2. Categorising JTAG devices

JTAG-enabled devices in the schematic should be identified by the user and assigned a BSDL file. It is recommended to obtain BSDL files from the appropriate part manufacturer's website. To associate a BSDL file with its component, press the *Add* button next to the JTAG devices list view (*see Figure 8*). The *Add JTAG Device* dialog box will open containing a device selector control and BSDL file selector control. Start typing a device reference into the device box and it will provide suggestions for devices in the circuit.

| Add JTAG De | evice                                 | ×      |

|-------------|---------------------------------------|--------|

| Device:     | IC1                                   | ~      |

| BSDL File:  | ects\JTAGDemoDesign\xc9536xl_cs48.bsd | Browse |

|             | ОК                                    | Cancel |

Figure 8: Associating a BSDL file to an IC in the schematic

The path to the BSDL file will be stored as a parameter of the device in the OrCAD Capture design. Any plain text file format is acceptable for use as a BSDL file and the plugin will automatically check that the file parses correctly. However the onus is on the user to ensure that the BSDL file is the correct one for the device chosen. An incorrect BSDL file may lead to incorrect and misleading results when using the XJTAG Chain Checker or XJTAG Access Viewer.

#### 4.3.3. Defining JTAG Chain(s)

As outlined above, a TAP (Test Access Port) comprises a minimum of four signals: TDI (Test Data In); TDO (Test Data Out); TCLK (Test Clock), and TMS (Test Mode Select). An optional fifth signal, nTRST (Test Reset) may also be present, which disables boundary scan when held low.

It is essential that the JTAG chain (TAP) is routed to the correct pins on each JTAG-enabled device in the chain. For the chain to function correctly it must be possible to trace a route from the board TDI pin (where the chain enters the board), into TDI and out of TDO of each JTAG device in turn and then to the board TDO pin (where the chain leaves the board). It is possible to implement more than one chain on a single design, however each JTAG-enabled device may only be connected to a single JTAG chain. The **XJTAG DFT Assistant for OrCAD Capture** software plugin provides a fully integrated way of ensuring scan chains are connected as intended and correctly.

In order to achieve this it is necessary to identify the TDI and TDO pins on each chain to determine how the PCB will be connected to the JTAG testing hardware. It is possible to define up to 4 scan chains in a single design. To select the TDI and TDO pins for each chain, click on the *Add* button next to the TDI and TDO list view, and this will open the *Add Chain* dialog box (*see Figure 9*).

| Add Cha | in      |    | ×      |

|---------|---------|----|--------|

| Name:   | Chain 1 |    |        |

| TDI:    | CN1.5   | ~  | Select |

| TDO:    | CN1.11  | ~  | Select |

|         |         | OK | Cancel |

|         |         |    |        |

Figure 9: Adding a boundary scan chain

The *Add Chain* dialog allows a name to be assigned to the chain and for the TDI and TDO pins to be selected from the pins on the board. Typically these pins will be test points or on a connector. To assign TDI either enter the device and pin designation directly in to the dialog box (for example, enter CN1.5 for Connector 1, Pin 5), or select a device and pin manually. If selecting manually, clicking the Select button will bring up the Select Device and Pin dialogue box showing all available devices. Selecting a device will reveal all available pins on that device, with their net designations (if included). Select a pin and press OK. Repeat this process to assign TDO.

Note: Once TDI or TDO have been assigned the Select Device and Pin dialogue box will default to the same component. This can be overridden if necessary by deleting the Device name in the Filter box. Once TDI and TDO have been assigned and BSDL files have been added for all JTAG-enabled devices in the chain, the plugin has enough information to automatically generate a JTAG chain route. The route is automatically generated each time the design is opened, therefore reflecting any changes made at the schematic level.

#### 4.3.4. Categorising passive devices

There are two reasons for categorising passive devices on the board. Firstly, it is common for passive devices, such as resistors and links, to be used in the JTAG chain. These devices need to be categorised to allow the JTAG chain to be auto-routed successfully. Secondly, categorising series resistors will allow the **XJTAG Access Viewer** tool to provide a more accurate indication of the extent of JTAG access on the board.

Passive devices are categorised by assigning them a passive device descriptor (PDD) file, in a similar way to JTAG devices and BSDL files, except that PDD files do not need to be supplied externally. PDD files for common cases, such as a series resistor, pull resistor, series and pull resistor packs etc., are included with the **XJTAG DFT Assistant for OrCAD Capture** plugin. More complex custom PDD files can be defined by the user through the plugin's interface to cover any possible passive device configuration.

There are two methods for categorising passive devices. Devices can be manually searched for and categorised by clicking the *View uncategorised devices* button to open the *Uncategorised Devices*

dialog (see Figure 10). Alternatively the XJTAG DFT Assistant for OrCAD Capture can suggest categorisations automatically by clicking the Suggest Categorisations button. The Suggest Categorisation dialog will provide PDD files for any passive devices that can be auto-categorised (see Figure 11).

| Filter: | All Boards                         | $\sim$          |           |           |  |

|---------|------------------------------------|-----------------|-----------|-----------|--|

| On      | y Show <u>A</u> ccessible Devices  |                 |           |           |  |

| ± Al    | Components                         |                 |           |           |  |

| Su      | ggested Bias Termination Resistors |                 |           |           |  |

| 🗄 Su    | ggested Connectors                 |                 |           |           |  |

| Su      | ggested Coupling Capacitors        |                 |           |           |  |

| 🗄 Su    | ggested Devices                    |                 |           |           |  |

| 🗄 Su    | ggested Diodes                     |                 |           |           |  |

| Su      | ggested Ferrite Beads              |                 |           |           |  |

| Su      | ggested Fuses                      |                 |           |           |  |

| ⊕ Su    | ggested Ignore Capacitors          |                 |           |           |  |

| Su      | ggested Inductors                  |                 |           |           |  |

| Su      | ggested Other Capacitors           |                 |           |           |  |

| 🕀 Su    | ggested Other Resistors            |                 |           |           |  |

| 🕀 Su    | ggested Pull Resistors             |                 |           |           |  |

| Su      | ggested Resistor Packs             |                 |           |           |  |

|         | ggested Series Resistors           | BOM Description | BOM Value | Pin Count |  |

|         | ·R5                                |                 | 1K        | 2         |  |

|         | R6                                 |                 | 1K        | 2         |  |

| -       | ·R7                                |                 | 1K        | 2         |  |

| -       | R9                                 |                 | 1K        | 2         |  |

|         | R19                                |                 | 1K        | 2         |  |

|         | -R20                               |                 | 1K        | 2         |  |

|         | -R24                               |                 | 1K        | 2         |  |

|         | -R34                               |                 | 100R      | 2         |  |

|         | -R35                               |                 | 470R      | 2         |  |

|         | ·R36                               |                 | 100R      | 2         |  |

|         | R37                                |                 | 51R       | 2         |  |

|         | -R38                               |                 | 51R       | 2         |  |

| Su      | ggested Unfitted Devices           |                 |           |           |  |

#### Figure 10: The Uncategorised Devices dialog box

| Reference  | Assign As | Definition        |   | Assign |

|------------|-----------|-------------------|---|--------|

| R1 (10K)   | Passive   | pull-resistor     | ~ |        |

| R2 (10K)   | Passive   | pull-resistor     | > |        |

| R3 (10K)   | Passive   | cselecto          | > |        |

| R4 (10K)   | Passive   | pull-resistor     | > |        |

| R5 (1K)    | Passive   | resistor          | > |        |

| R6 (1K)    | Passive   | resistor          | > | 2      |

| R7 (1K)    | Passive   | resistor          | > |        |

| R8 (10K)   | Passive   | pull-resistor     | > |        |

| R9 (1K)    | Passive   | resistor          | > |        |

| R10 (100R) | Passive   | <select></select> | > |        |

| R11 (820R) | Passive   | <select></select> | > |        |

| R12 (150R) | Passive   | <select></select> | > |        |

| R13 (150R) | Passive   | <select></select> | > |        |

| R14 (150R) | Passive   | <select></select> | ~ |        |

| R15 (150R) | Passive   | <select></select> | ~ |        |

| R16 (1K)   | Passive   | pull-resistor     | ~ |        |

| R17 (1K)   | Passive   | pull-resistor     | ~ |        |

| R18 (1K)   | Passive   | pull-resistor     | ~ |        |

| R19 (1K)   | Passive   | resistor          | ~ | 2<br>2 |

| R20 (1K)   | Passive   | resistor          | ~ |        |

| R21 (10K)  | Passive   | pull-resistor     | ~ |        |

| R22 (51R)  | Passive   | <select></select> | ~ |        |

| R23 (1K)   | Passive   | pull-resistor     | ~ |        |

Figure 11: The Suggest Categorisation dialog box

To avoid categorising passive devices that will not affect the extent of JTAG access, the *Suggest Categorisation* dialog is limited to those devices already on nets with JTAG access.

To uncategorise an already categorised device, press the *View categorised devices* button which will bring up a list of all passive devices categorised so far. From here a device, or group of devices, can be selected and uncategorised.

#### 4.3.5. Manually creating a passive device

To manually create a passive device (using a new PDD file) open the *Uncategorised Devices* dialog and select a device, either by navigating the tree view or typing the device reference into the filter box. Clicking the *Only Show Accessible Devices* checkbox will toggle between showing all devices in the circuit or only showing devices on nets with JTAG access. Once a device, or group of devices, is selected press the *Categorise As Passive* button to open the *Assign Device* dialog (see *Figure 12*).

| Assign Device as Pas   | sive: R37   |    | ×      |   |

|------------------------|-------------|----|--------|---|

| Known Device Files     |             |    |        |   |

| File                   | Description |    |        |   |

| resistor.pdd (Library) |             |    |        |   |

|                        |             |    |        |   |

|                        |             |    |        |   |

|                        |             |    |        |   |

|                        |             |    |        |   |

| 🚼 Create File 🏼 🎦      | Browse      |    |        |   |

| Connection Device P    | roperties   |    |        |   |

| Show Warnings          |             |    |        |   |

| Device Note            |             |    |        |   |

|                        |             |    |        | ٦ |

|                        |             |    |        |   |

|                        |             |    |        |   |

|                        |             |    |        |   |

|                        |             | ОК | Cancel |   |

Figure 12: Assigning a device as a passive

The top half of the dialog will provide suggestions for possible PDD files that match the parameters of the device. Selecting one of these and pressing OK will categorise the device. If no suitable PDD file is present in the top list there are the options to browse for an existing PDD file that was created previously or to create a new one. Pressing the *Create File* button will open the New PDD File Dialog (*see Figure 13*).

| New PDD File             |                                                      |                                                                                            |                          |                        |     | ×      |

|--------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------|------------------------|-----|--------|

| Device Details           |                                                      | Connection List                                                                            |                          |                        |     |        |

| File Name<br>Description | 8 Pin Resistor Pack.pdd  8 pin resistor pack  Select | Connection Type<br>Connect<br>Connect<br>Connect<br>Connect<br>X Remove<br>Add Connections | From<br>1<br>2<br>3<br>4 | To<br>8<br>7<br>6<br>5 |     |        |

|                          |                                                      | Connect v                                                                                  | Т.                       | ō                      | Add | _      |

|                          |                                                      |                                                                                            |                          |                        | ОК  | Cancel |

Figure 13: Creating a new PDD file

To create a new PDD file, enter a filename and (optionally) some description text and then add connections between pins. Connections can be of two types, either a simple connection (where the two pins are electrically linked or there is a low resistance value between them) or a pull connection (for pull resistors). Once a type is selected, and the pin numbers have been entered, press *Add* to add the connection to the list. Once all connections are added, click OK to create the new file.

Connections which do not fall into these types (e.g. terminations) should be left uncategorised – if the project is exported into **XJDeveloper** they can be set up there.

### 4.4. Check JTAG Chain

Once setup is complete, clicking on the *Check Chain* button will initialise the **XJTAG Chain Checker**. This will open the *Chain Check Results* dialog box (*see Figure 14*), giving a breakdown of any potential errors or causes for concern in the JTAG chains that have been defined.

The errors and warnings reported by the **XJTAG Chain Checker** are split into 3 categories; TAP net connection errors, TAP net termination errors and compliance pin errors. Connection errors are problems that prevent a JTAG chain being routed successfully and are classed as fatal errors as they will prevent any JTAG access through that chain. Termination errors are caused by TAP nets not being terminated to power or ground properly, potentially causing signal integrity issues. The errors and warnings will make recommendations for how best to prevent this. Compliance pins are pins on JTAG devices that must be set correctly to enable the device's boundary scan operation. The pins and values required are set out in the *Compliance Patterns* section of the BSDL file and the compliance pin errors will report any errors in the circuit design that prevent these pins being set correctly.

| TAP             | Connections                                                                                                                                                                                                                 |              |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Type<br>Success | Detail<br>TAP connections passed                                                                                                                                                                                            |              |

| ТАР             | Terminations                                                                                                                                                                                                                | DFT Gu       |

| Туре            | Detai                                                                                                                                                                                                                       |              |

| Error           | TDO signal on chain chain 1 (net XTDO) should be pulled to power with resistor between 1 k $\Omega$ and 50 k $\Omega$                                                                                                       |              |

| Error<br>Error  | TDO signal on chain chain 2 (net CTDO) should be pulled to power with resistor between 1 kΩ and 50 kΩ.<br>TRST signal on chain chain 2 (net TRST) should be pulled to power or ground with resistor between 1 kΩ and 50 kΩ. |              |

| Error           | TCK signal on than than 2 (her TCS) should be pulled to power or glound with resistor between 1 ku2 and 30 ku2.<br>TCK signal on net TCK has no resistor to ground. Recommended value is between 25 Ω and 150 Ω.            |              |

|                 | TDO signal on chain chain 1 has series resistor R37 with value of 51 $\Omega$ to TDO pin of device IC1. Recommended value is be                                                                                             |              |

| Warning         | TDO signal on chain chain 2 has series resistor R38 with value of 51 $\Omega$ to TDO pin of device IC2. Recommended value is be                                                                                             | tween 10Ω an |

|                 |                                                                                                                                                                                                                             |              |

| Com             | pliance Pins                                                                                                                                                                                                                |              |

| Com             | pliance Pins                                                                                                                                                                                                                |              |

| Туре            |                                                                                                                                                                                                                             |              |

| Туре            | Detai                                                                                                                                                                                                                       |              |

Figure 14: The Chain Check Results Dialog box

The full list of errors and warnings that are detected are shown below:

| IAP IIE | t connection errors                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------|

| •       | TAP net (TDI, TDO, TMS, TCLK or TRST) connected to the wrong pin(s) with respect to the appropriated RSDL file(c) |

|         | with respect to the associated BSDL file(s)                                                                       |

| •       | TAP net connected to a power or ground net                                                                        |

| •       | Two different TAP nets connected together                                                                         |

|         | Loop in a JTAG chain                                                                                              |

| •       | Two TDI pins connected to the same net                                                                            |

| •       | Unable to route JTAG chain for some other reason                                                                  |

| IAP ne  | t connection warnings                                                                                             |

| •       | All devices in chain do not share the same TMS or TCK                                                             |

|         | t termination errors                                                                                              |

| •       | TDI, TDO or TMS not pulled to power                                                                               |

| •       | TRST not pulled to ground                                                                                         |

| •       | No series resistor on TDO                                                                                         |

| •       | TCK not terminated to ground with a resistor and capacitor                                                        |

| TAP ne  | t termination warnings                                                                                            |

| •       | TDI, TDO or TMS pulled to power with a resistor of the wrong value                                                |

| •       | TRST pulled to ground with a resistor of the wrong value                                                          |

| •       | TCK terminated with a resistor/capacitor of the wrong value                                                       |

| Compli  | ance pin errors                                                                                                   |

| •       | Compliance pin tied the wrong way                                                                                 |

| •       | Compliance pin pulled the wrong way with no other device on the net                                               |

| •       | Compliance pin not connected                                                                                      |

| Compli  | ance pin warnings                                                                                                 |

| •       | Compliance pin not tied or pulled                                                                                 |

Full list of faults detected by XJTAG DFT Assistant for OrCAD Capture

Note: The termination check and compliance pin check will not run if there are TAP net connection errors.

#### 4.5. XJTAG Access Viewer

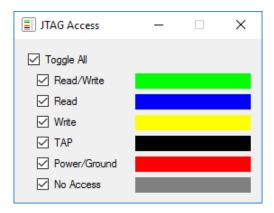

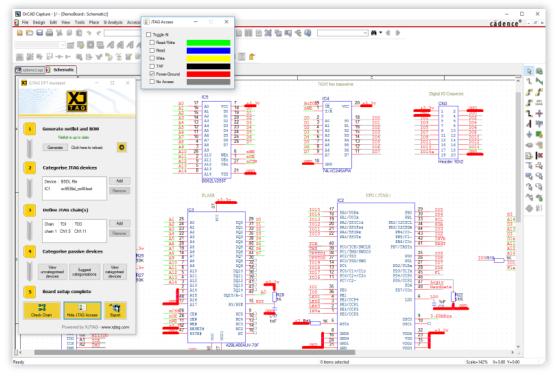

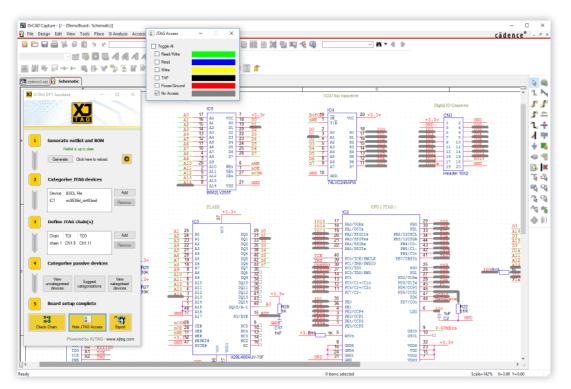

At any stage of the board setup, clicking on the *Show JTAG Access* button will highlight the JTAG access on each page of the schematic diagram. This feature shows the best level of access available on each net, as long as all JTAG devices categorised so far are connected up correctly. The nets will be colour-coded, as shown in *Figure 15*. The nets accessible to boundary scan testing will be highlighted using these colour codes, as shown in *Figure 16*.

Figure 15: Colour-coded nets showing boundary scan access

Figure 16: Screenshot showing colour-coded boundary scan access

Ticking and unticking on access types in the *JTAG Access Legend* toggles the thickness of those nets in the design (see *Figures 17-18*).

Figure 17: Power/Ground nets only

Figure 18: Nets with no boundary scan access

Pressing the *Hide JTAG Access* button, closing the *JTAG Access Legend* or *XJTAG DFT Assistant* window, closing the design or closing OrCAD Capture will return all nets to their original colours and thickness.

### 5. Export XJDeveloper Project

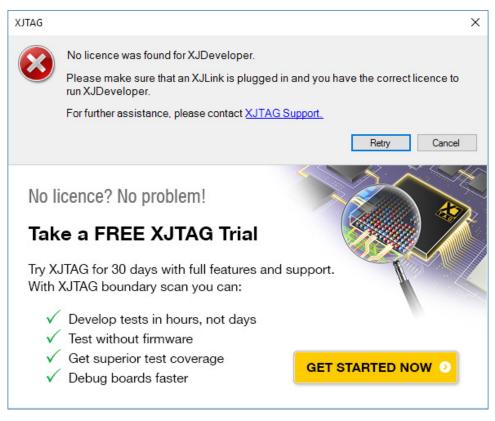

At any stage, users with a licence from XJTAG can export the information they have entered as an **XJDeveloper** project. By clicking on *Export XJDeveloper Project*, the **XJTAG DFT Assistant for OrCAD Capture** will look for a valid **XJDeveloper** licence. If no licence is detected, the following box will appear (see *Figure 19*):

Figure 19: Missing XJDeveloper licence dialog box

If no valid **XJDeveloper** licence is available, click on *Get Started Now* to open a webpage detailing the free evaluation offer on XJTAG's website.

Please note, the exported project requires V3.4 or higher of XJDeveloper

### 5.1. Boundary Scan test development

**XJDeveloper** is XJTAG's Integrated Development Environment (IDE) for the development and execution of interconnection and functional tests run over Boundary Scan. It provides all the functionality needed to execute boundary scan tests on a prototype board, as well as production tests in a manufacturing environment.

**XJDeveloper** includes an extensive library of functional tests for non JTAG-enabled devices. It also includes a powerful test development language called *XJEase*, which makes it easy to develop further tests and apply them through an *XJLink2 Controller*.

## 5.2. Migrating a project to XJDeveloper

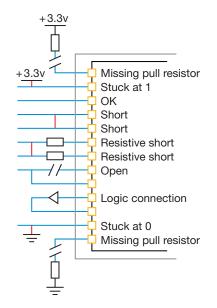

The setup process completed within the **XJTAG DFT Assistant for OrCAD Capture** can be exported as an **XJDeveloper** project, and simply opened from within **XJDeveloper**. The user can then continue with the board setup process, by categorising the remaining non JTAG-enabled devices which have not been categorised in the *XJTAG DFT Assistant*. A full interconnectivity test can then be carried out on the PCB once manufactured, to identify a wide range of manufacturing faults. The full list of faults that can be detected using XJTAG's boundary scan technology is illustrated in *Figure 20*.

Figure 20: The full range of faults detectable using XJTAG's boundary scan technology

## 6. Troubleshooting

#### • The XJTAG DFT Assistant plugin fails to install

Please check you have the correct version of OrCAD Capture installed. The plugin supports Capture 17.2 or later. The plugin also requires the .NET Framework version 4.7.1 or later. Download it here: <a href="https://www.microsoft.com/en-us/download/details.aspx?id=56116">https://www.microsoft.com/en-us/download/details.aspx?id=56116</a>. If the installer still does not work please contact *support@xjtag.com*.

#### • Error while generating netlist

If generating a netlist using the internal netlist builder is failing, try generating a netlist directly in OrCAD Capture (orPcad64.dll orRinf64.dll recommended) and select to copy that netlist file in the XJTAG DFT Assistant plugin settings. If errors still occur please contact <u>support@xjtag.com</u> with details of the specific error you are seeing.

#### • Registration reports "Unable to communicate with XJTAG server"

This error means the *XJTAG DFT Assistant* is unable to connect to the internet. An active internet connection is required in order to register for the *XJTAG DFT Assistant* plugin. Once successfully registered, no further internet connection is required.

• Chain Check – "Fatal Error: Cannot find a TDI pin or the final TDO pin connected to pin X.x."

This error means the chain check is unable to find a valid route for the JTAG chain. Please check that the TDI and TDO pins you have provided are correct. The most common cause of this error is an uncategorised passive device in the JTAG chain. The pin listed in the error is the last point in the JTAG chain reached before the auto-route failed, so this is a useful place to look for the issue. See *Section 4.3.4* for a guide on categorising passive devices.

#### Chain Check – Termination or Compliance errors are reported incorrectly

The chain check uses a variety of patterns to identify pull resistors on the schematic automatically. However this cannot always correctly identify all components. Specifically resistor references that do not begin with an R, or BOM values that contain other information apart from just a resistance, can cause problems. Results can always be improved by categorising any pull resistors or resistor packs on the TAP nets. See *Section 4.3.4* for a guide on categorising passive devices. Please contact *support@xjtag.com* if you are still having issues.

#### • The JTAG Access colour scheme is stuck on

If the JTAG access colours are left on when OrCAD Capture is shut down, they will remain on the next time OrCAD is opened. To return all nets to their normal colours simply open the *XJTAG DFT Assistant* window and click "Generate". This will return all wires to their state before the JTAG Access colours were enabled.

• **Project files appear modified in source control systems after using the XJTAG DFT Assistant** The plugin saves categorisations and net colour/width information to project files so they will show up as modified after the plugin is used. If using a source control system please be aware of this, and if changes are discarded then categorisation information will be lost.

#### All categorisations are removed after moving the OrCAD Capture project

BSDL files and PDD files used for categorisation are stored in a hidden folder called XJTAG inside the project directory. If this folder is not moved with the project then unfortunately all categorisations will be lost. Make sure to copy this folder with the project if you wish to keep your categorisation information.

Any other issues relating to the XJTAG DFT Assistant, or if you would like to submit a bug or feature request, please contact **support@xjtag.com**.

## 7. Further reading

For more information on XJTAG's boundary scan technology, visit **www.xjtag.com**. For an extensive guide to Design For Test best-practices for boundary scan testing, visit: **www.xjtag.com/about-jtag/design-for-test-guidelines**

## About XJTAG

XJTAG is a world leading supplier of JTAG boundary-scan hardware and software tools. The company focuses on innovative product development and high quality technical support.

XJTAG products use IEEE Std.1149.x (JTAG boundary-scan) to enable engineers to debug, test and program electronic circuits quickly and easily. This can significantly shorten the electronic design, development and manufacturing processes.

XJTAG, based in Cambridge, UK, released version 1.0 of its boundary-scan tools in 2003 and starting from the UK, XJTAG has expanded and is now a business with multi-million dollar worldwide sales. XJTAG was the first boundary-scan solution to offer a common platform for use by design and development engineers, test engineers, contract manufacturers and field test engineers, providing testing of not only JTAG-enabled devices but non-JTAG devices as well. This change of emphasis towards test re-use and usability has driven the boundary-scan market forward, as board designers realised that they can have the test equipment on their benches and then re-use tests at production time.

XJTAG believes in being open – clients can see and edit the script files that are used to test for non-JTAG devices. If a revised device comes along, or the client has a problem, they can alter or debug the test themselves if they do not wish to (or are unable to) involve XJTAG.

Clients across a wide range of industries benefit from using XJTAG products. These include aerospace, automotive, defence, medical, manufacturing, networking and telecommunications. The company sells and supports its products worldwide and works closely with over 50 experienced and professional distributors and technology partners across the globe. XJTAG is part of Cambridge Technology Group.

#### **UK Headquarters**

XJTAG CamTech House 137 Cambridge Road Milton Cambridge CB24 6AZ United Kingdom

Tel: +44 (0)1223 223007 Email: enquiries@xjtag.com Web site: www.xjtag.com

#### Third Party Software Attributions, Copyrights, Licenses

#### Autofac

Copyright © 2014 Autofac Project License: MIT License (MIT)

#### MIT License (MIT)

Permission is hereby granted, free of charge, to any person obtaining a copy of this software and associated documentation files (the "Software"), to deal in the Software without restriction, including without limitation the rights to use, copy, modify, merge, publish, distribute, sublicense, and/or sell copies of the Software, and to permit persons to whom the Software is furnished to do so, subject to the following conditions:

The above copyright notice and this permission notice shall be included in all copies or substantial portions of the Software.

THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE SOFTWARE.

#### CefSharp

Copyright © 2010-2018 The CefSharp Authors

Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

- Redistributions of source code must retain the above copyright notice, this list

of conditions and the following disclaimer.

- Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution.

- Neither the name of Google Inc. nor the name Chromium Embedded Framework nor the name CefSharp nor the names of its contributors may be used to endorse or promote products derived from this software without specific prior written permission.

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

#### DotNetZip

DotNetZip - Copyright (c) 2006 - 2011 Dino Chiesa DotNetZip - Copyright (c) 2006, 2007, 2008, 2009 Dino Chiesa and Microsoft Corporation.

#### protobuf-net

Copyright 2008 Marc Gravell License: Apache License, Version 2.0 Apache License Version 2.0 January 2004 http://www.apache.org/licenses/

TERMS AND CONDITIONS FOR USE, REPRODUCTION, AND DISTRIBUTION

#### 1. Definitions.

"License" shall mean the terms and conditions for use, reproduction, and distribution as defined by Sections 1 through 9 of this document.

"Licensor" shall mean the copyright owner or entity authorized by the copyright owner that is granting the License.

"Legal Entity" shall mean the union of the acting entity and all other entities that control, are controlled by, or are under common control with that entity. For the purposes of this definition, "control" means (i) the power, direct or indirect, to cause the direction or management of such entity, whether by contract or otherwise, or (ii) ownership of fifty percent (50%) or more of the outstanding shares, or (iii) beneficial ownership of such entity.

"You" (or "Your") shall mean an individual or Legal Entity exercising permissions granted by this License.

"Source" form shall mean the preferred form for making modifications, including but not limited to software source code, documentation source, and configuration files.

"Object" form shall mean any form resulting from mechanical transformation or translation of a Source form, including but not limited to compiled object code, generated documentation, and conversions to other media types.

"Work" shall mean the work of authorship, whether in Source or Object form, made available under the License, as indicated by a copyright notice that is included in or attached to the work (an example is provided in the Appendix below).

"Derivative Works" shall mean any work, whether in Source or Object form, that is based on (or derived from) the Work and for which the editorial revisions, annotations, elaborations, or other modifications represent, as a whole, an original work of authorship. For the purposes of this License, Derivative Works shall not include works that remain separable from, or merely link (or bind by name) to the interfaces of, the Work and Derivative Works thereof.

"Contribution" shall mean any work of authorship, including the original version of the Work and any modifications or additions to that Work or Derivative Works thereof, that is intentionally submitted to Licensor for inclusion in the Work by the copyright owner or by an individual or Legal Entity authorized to submit on behalf of the copyright owner. For the purposes of this definition, "submitted" means any form of electronic, verbal, or written communication sent to the Licensor or its representatives, including but not limited to communication on electronic mailing lists, source code control systems, and issue tracking systems that are managed by, or on behalf of, the Licensor for the purpose of discussing and improving the Work, but excluding communication that is conspicuously marked or otherwise designated in writing by the copyright owner as "Not a Contribution."

"Contributor" shall mean Licensor and any individual or Legal Entity on behalf of whom a Contribution has been received by Licensor and subsequently incorporated within the Work.

2. Grant of Copyright License. Subject to the terms and conditions of this License, each Contributor hereby grants to You a perpetual, worldwide, non-exclusive, no-charge, royalty-free, irrevocable copyright license to reproduce, prepare Derivative Works of, publicly display, publicly perform, sublicense, and distribute the Work and such Derivative Works in Source or Object form.

3. Grant of Patent License. Subject to the terms and conditions of this License, each Contributor hereby grants to You a perpetual, worldwide, non-exclusive, nocharge, royalty-free, irrevocable (except as stated in this section) patent license to make, have made, use, offer to sell, sell, import, and otherwise transfer the Work, where such license applies only to those patent claims licensable by such Contributor that are necessarily infringed by their Contribution(s) alone or by combination of their Contribution(s) with the Work to which such Contribution(s) was submitted. If You institute patent litigation against any entity (including a cross-claim or counterclaim in a lawsuit) alleging that the Work or a Contribution incorporated within the Work constitutes direct or contributory patent infringement, then any patent licenses granted to You under this License for that Work shall terminate as of the date such litigation is filed.

4. Redistribution. You may reproduce and distribute copies of the Work or Derivative Works thereof in any medium, with or without modifications, and in Source or Object form, provided that You meet the following conditions:

1. You must give any other recipients of the Work or Derivative Works a copy of this License; and

2. You must cause any modified files to carry prominent notices stating that You changed the files; and

3. You must retain, in the Source form of any Derivative Works that You distribute, all copyright, patent, trademark, and attribution notices from the Source form of the Work, excluding those notices that do not pertain to any part of the Derivative Works; and

4. If the Work includes a "NOTICE" text file as part of its distribution, then any Derivative Works that You distribute must include a readable copy of the attribution notices contained within such NOTICE file, excluding those notices that do not pertain to any part of the Derivative Works, in at least one of the following places: within a NOTICE text file distributed as part of the Derivative Works; within the Source form or documentation, if provided along with the Derivative Works; or, within a display generated by the Derivative Works, if and wherever such third-party notices normally appear. The contents of the NOTICE file are for informational purposes only and do not modify the License. You may add Your own attribution notices within Derivative Works, that You distribute, alongside or as an addendum to the NOTICE text from the Work, provided that such additional attribution notices cannot be construed as modifying the License.

You may add Your own copyright statement to Your modifications and may provide additional or different license terms and conditions for use, reproduction, or distribution of Your modifications, or for any such Derivative Works as a whole, provided Your use, reproduction, and distribution of the Work otherwise complies with the conditions stated in this License.

5. Submission of Contributions. Unless You explicitly state otherwise, any Contribution intentionally submitted for inclusion in the Work by You to the Licensor shall be under the terms and conditions of this License, without any additional

terms or conditions. Notwithstanding the above, nothing herein shall supersede or modify the terms of any separate license agreement you may have executed with Licensor regarding such Contributions.

6. Trademarks. This License does not grant permission to use the trade names, trademarks, service marks, or product names of the Licensor, except as required for reasonable and customary use in describing the origin of the Work and reproducing the content of the NOTICE file.

7. Disclaimer of Warranty. Unless required by applicable law or agreed to in writing, Licensor provides the Work (and each Contributor provides its Contributions) on an "AS IS" BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied, including, without limitation, any warranties or conditions of TITLE, NON-INFRINGEMENT, MERCHANTABILITY, or FITNESS FOR A PARTICULAR PURPOSE. You are solely responsible for determining the appropriateness of using or redistributing the Work and assume any risks associated with Your exercise of permissions under this License.

8. Limitation of Liability. In no event and under no legal theory, whether in tort (including negligence), contract, or otherwise, unless required by applicable law (such as deliberate and grossly negligent acts) or agreed to in writing, shall any Contributor be liable to You for damages, including any direct, indirect, special, incidental, or consequential damages of any character arising as a result of this License or out of the use or inability to use the Work (including but not limited to damages for loss of goodwill, work stoppage, computer failure or malfunction, or any and all other commercial damages or losses), even if such Contributor has been advised of the possibility of such damages.

9. Accepting Warranty or Additional Liability. While redistributing the Work or Derivative Works thereof, You may choose to offer, and charge a fee for, acceptance of support, warranty, indemnity, or other liability obligations and/or rights consistent with this License. However, in accepting such obligations, You may act only on Your own behalf and on Your sole responsibility, not on behalf of any other Contributor, and only if You agree to indemnify, defend, and hold each Contributor harmless for any liability incurred by, or claims asserted against, such Contributor by reason of your accepting any such warranty or additional liability.

END OF TERMS AND CONDITIONS

#### Scintilla.NET

Permission to use, copy, modify, and distribute this software and its documentation for any purpose and without fee is hereby granted, provided that the above copyright notice appear in all copies and that both that copyright notice and this permission notice appear in supporting documentation.

GARRETT SERACK AND ALL EMPLOYERS PAST AND PRESENT DISCLAIM ALL WARRANTIES WITH REGARD TO THIS SOFTWARE, INCLUDING ALL IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS, IN NO EVENT SHALL GARRETT SERACK AND ALL EMPLOYERS PAST AND PRESENT BE LIABLE FOR ANY SPECIAL, INDIRECT OR CONSEQUENTIAL DAMAGES OR ANY DAMAGES WHATSOEVER RESULTING FROM LOSS OF USE, DATA OR PROFITS, WHETHER IN AN ACTION OF CONTRACT, NEGLIGENCE OR OTHER TORTIOUS ACTION, ARISING OUT OF OR IN CONNECTION WITH THE USE OR PERFORMANCE OF THIS SOFTWARE.

#### SourceGrid

Copyright (c) 2011 Davide Icardi License: MIT License (MIT)