# XJTAG<sup>®</sup> XJAccelerator Hardware

# User Guide

Version 2

# Table of Contents

#### SECTION

| 1. Introduction                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------|

| 2. XJAccelerator Block Diagram                                                                                     |

| 3. Powering the XJAccelerator                                                                                      |

| 4. XJLink2 Connector Pinout (P1)5                                                                                  |

| 5. I/O Connectors                                                                                                  |

| 6. I/O Pinout                                                                                                      |

| 7. I/O Voltage Domains                                                                                             |

| 8. I/O Electrical Characteristics                                                                                  |

| 9. Setting the I/O into a Tristate Condition                                                                       |

| 10. Routing TDO                                                                                                    |

| 11. Passthrough Mode                                                                                               |

| 12. Programming FPGA Images10                                                                                      |

| 13. Protection Boards                                                                                              |

|                                                                                                                    |

| Figure 1 – XJAccelerator Board                                                                                     |

| Figure 2 – XJAccelerator Block Diagram                                                                             |

| Figure 3 – DC Power Input                                                                                          |

| Figure 4 – XJLink Connector                                                                                        |

| Figure 5 – I/O Connector                                                                                           |

| Figure 6 – Rotary switches and connectors                                                                          |

| Figure 7 – TDO Routing                                                                                             |

| Figure 8 – Locating the Links to Configure Passthrough Mode9                                                       |

| Figure 9 – XJAccelerator with 3 protection boards10                                                                |

| Table 1 VII ink2 Input Connector Disput                                                                            |

| Table 1 – XJLink2 Input Connector Pinout                                                                           |

| Table 2 – P2 I/O Pinout    6                                                                                       |

|                                                                                                                    |

| Table 4 – P4 I/O Pinout  6                                                                                         |

| Table 5 – I/O Logic Thresholds (LVCMOS standards)    7      Table 6 – I/O Logic Thresholds (LVCMOS standards)    7 |

| Table 6 – FPGA Drive Strength Options                                                                              |

| Table 7 – Placing the I/O into a Tristate Mode                                                                     |

| Table 8 – Selecting the Source of TDO                                                                              |

| Table 9 – Hardware Configuration to Route Directly to the XJLink2      9                                           |

| Table 10 – XJAccelerator Active Protector ratings 10                                                               |

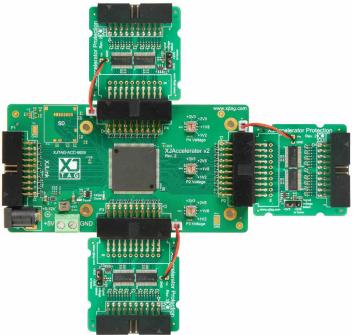

# 1. Introduction

The XJAccelerator is a configurable FPGA board with three I/O connectors that can run on different voltage domains. The board's main uses are:

- high-speed programming of flash memories when a PCB doesn't have a suitable FPGA for accelerated programming.

- high-speed programming of multiple devices concurrently, including when they are different device types with different interfaces.

- to act as a JTAG Multiplexer (scan bridge).

- to act as a mini I/O expander.

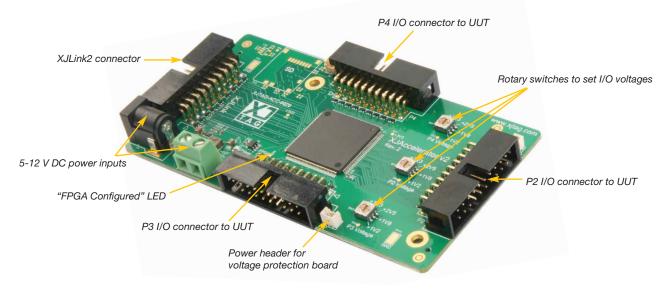

Figure 1 – XJAccelerator Board

The board's interfaces are:

- XJLink2 connector

- 5-12 V DC power inputs (use either)

- P2 I/O connector to UUT

- P3 I/O connector to UUT

- P4 I/O connector to UUT

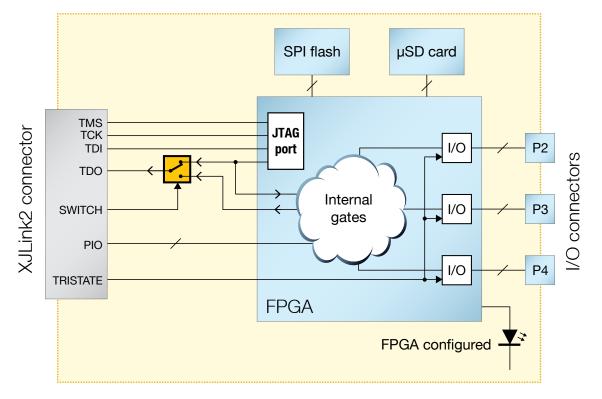

When used for accelerated programming, the data can be streamed to the FPGA using JTAG, or retrieved from a micro SD card. The I/O connectors provide the interfaces to the devices to be programmed.

When used as a JTAG multiplexer, the UUT's JTAG chains are connected to the XJAccelerator's I/O connectors, and the TDO Switch should be set so that the XJLink2 receives JTAG data from the FPGA's logic instead of its JTAG port (see *Routing TDO* on page 8).

# 2. XJAccelerator Block Diagram

Figure 2 – XJAccelerator Block Diagram

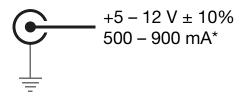

### 3. Powering the XJAccelerator

The board can be powered from either a DC input socket or screw down terminals. In either case, the input voltage must be between 5 and 12 V DC.

Connector type: 2.1 mm central pin, 5.5 mm outer diameter, 9.5 mm barrel length. Suitable mating plug: Farnell 224923, Digi-Key EP501A-ND, RS 487-858.

Figure 3 – DC Power Input

\* 500 mA is suitable for most setups. However, the current requirement may exceed this depending on output loading and how the FPGA is configured.

# 4. XJLink2 Connector Pinout (P1)

The XJLink2 connects to the board using P1. The JTAG interface and this connector's PIO operate at 3.3 V, which cannot be changed. The pinout is shown in Table 1.

| Pin | Signal   | Function                                                                                          |

|-----|----------|---------------------------------------------------------------------------------------------------|

| 1   | TRISTATE | High: puts FPGA I/O into tristate mode. (PCB has a 4k7 pulldown)                                  |

| 2   | SWITCH   | Low: TDO comes from the FPGA's JTAG port only<br>High: TDO comes from the FPGA's internal logic   |

| 3   | TDO      | From either the FPGA's JTAG port or the FPGA's internal logic depending on state of signal SWITCH |

| 4   | PIO 4    | PIO connected to FPGA bank 2 pin 66                                                               |

| 5   | TDI      | JTAG TDI signal from the XJLink2                                                                  |

| 6   | PIO 6    | PIO connected to FPGA bank 2 pin 62                                                               |

| 7   | TMS      | JTAG TMS signal from the XJLink2                                                                  |

| 8   | PIO 8    | PIO connected to FPGA bank 2 pin 61                                                               |

| 9   | TCK      | JTAG TCK signal from the XJLink2                                                                  |

| 10  | GND      |                                                                                                   |

| 11  | PIO 11   | PIO connected to FPGA bank 2 pin 59                                                               |

| 12  | PIO 12   | PIO connected to FPGA bank 2 pin 58                                                               |

| 13  | PIO 13   | PIO connected to FPGA bank 2 pin 57                                                               |

| 14  | PIO 14   | PIO connected to FPGA bank 2 pin 56                                                               |

| 15  | PIO 15   | PIO connected to FPGA bank 2 pin 55                                                               |

| 16  | PIO 16   | PIO connected to FPGA bank 2 pin 51                                                               |

| 17  | PIO 17   | PIO connected to FPGA bank 2 pin 50                                                               |

| 18  | PIO 18   | PIO connected to FPGA bank 2 pin 48                                                               |

| 19  | PIO 19   | PIO connected to FPGA bank 2 pin 47                                                               |

| 20  | GND      |                                                                                                   |

Table 1 – XJLink2 Input Connector Pinout

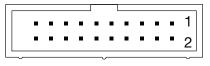

Connector type: keyed 20-pin 0.1" pitch.

Suitable mating connector: Farnell 1200505, Digi-Key 1195-7010-ND, RS 426-3766.

Figure 4 – XJLink Connector

# 5. I/O Connectors

The board has three I/O connectors, P2 – P4, that connect to PIO on the FPGA.

Pins 10 and 20 are connected to ground.

Connector type: keyed 20-pin 0.1" pitch.

Suitable mating connector: Farnell 1200505, Digi-Key 1195-7010-ND, RS 426-3766.

Figure 5 – I/O Connector

# 6. I/O Pinout

| Connector Pin | FPGA Pin<br>(bank 0) | Connector Pin | FPGA Pin<br>(bank 0) |

|---------------|----------------------|---------------|----------------------|

| 1             | 143                  | 2             | 142                  |

| 3             | 141                  | 4             | 111                  |

| 5             | 138                  | 6             | 117                  |

| 7             | 134                  | 8             | 118                  |

| 9             | 127                  | 10            | GND                  |

| 11            | 119                  | 12            | 123                  |

| 13            | 124                  | 14            | 126                  |

| 15            | 132                  | 16            | 133                  |

| 17            | 137                  | 18            | 139                  |

| 19            | 140                  | 20            | GND                  |

#### Table 2 – P2 I/O Pinout

| Connector Pin | FPGA Pin<br>(bank 1) | Connector Pin | FPGA Pin<br>(bank 1) |  |

|---------------|----------------------|---------------|----------------------|--|

| 1             | 104                  | 2             | 102                  |  |

| 3             | 101                  | 4             | 100                  |  |

| 5             | 99                   | 6             | 98                   |  |

| 7             | 97                   | 97 8          |                      |  |

| 9             | 93                   | 10            | GND                  |  |

| 11            | 88                   | 12            | 92                   |  |

| 13            | 85                   | 14            | 87                   |  |

| 15            | 83                   | 16            | 84                   |  |

| 17            | 17 81                |               | 82                   |  |

| 19            | 80                   | 20            | GND                  |  |

#### Table 3 – P3 I/O Pinout

| Connector Pin | FPGA Pin<br>(bank 3) | Connector Pin | FPGA Pin<br>(bank 3) |  |

|---------------|----------------------|---------------|----------------------|--|

| 1             | 35                   | 2             | 34                   |  |

| 3             | 33                   | 4             | 32                   |  |

| 5             | 30                   | 6             | 29                   |  |

| 7             | 7 26                 |               | 24                   |  |

| 9             | 23                   | 10            | GND                  |  |

| 11            | 12                   | 12            | 14                   |  |

| 13            | 10                   | 14            | 11                   |  |

| 15            | 6                    | 16            | 7                    |  |

| 17            | 2                    | 18            | 5                    |  |

| 19            | 1                    | 20            | GND                  |  |

#### Table 4 – P4 I/O Pinout

# 7. I/O Voltage Domains

The three I/O connectors can have their voltages configured independently to match the I/O standard required. These voltages provided by the hardware are adjusted by changing the rotary switches near the connectors, as shown in Figure 6. The switches and connectors all have labels (e.g. P4 and P4 voltage) to allow you to easily identify which switch corresponds to which connector. These switches can be adjusted with a flathead screwdriver so that the arrow on the groove points to the required voltage.

The factory default setting for every bank is 3V3.

Figure 6 – Rotary switches and connectors

# 8. I/O Electrical Characteristics

The characteristics of the signals on the three I/O connectors will be determined by how the FPGA has been configured. However, it is normal to use the LVCMOS standards for the I/O, in which case the logic thresholds will be as listed in Table 7 (voltages stated are valid across all possible drive strengths). Their values are dependent on the voltage domain that has been selected for that bank of I/O.

| Voltage Domain | V <sub>IL</sub> (min) | V <sub>IL</sub> (max) | V <sub>IH</sub> (min) | V <sub>IH</sub> (max) | V <sub>OL</sub> (max) | V <sub>OH</sub> (min) |

|----------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 3V3            | -0.5                  | 0.80                  | 2.0                   | 4.1                   | 0.40                  | 2.90                  |

| 2V5            | -0.5                  | 0.70                  | 1.7                   | 4.1                   | 0.40                  | 2.10                  |

| 1V8            | -0.5                  | 0.38                  | 0.8                   | 4.1                   | 0.45                  | 1.35                  |

| 1V5            | -0.5                  | 0.38                  | 0.8                   | 4.1                   | 0.38                  | 1.13                  |

The maximum current capability of the pins is dependent on the drive strength set when the FPGA was configured. Possible options are listed in Table 8; they are dependent on the I/O interface voltage and the connector being used.

| Voltage Domain | P2 (mA)                | P3 (mA)                | P4 (mA)                |

|----------------|------------------------|------------------------|------------------------|

| 3V3            | 2, 4, 6, 8, 12, 16, 24 | 2, 4, 6, 8, 12, 16, 24 | 2, 4, 6, 8, 12, 16, 24 |

| 2V5            | 2, 4, 6, 8, 12, 16     | 2, 4, 6, 8, 12, 16, 24 | 2, 4, 6, 8, 12, 16, 24 |

| 1V8            | 2, 4, 6, 8, 12, 16     | 2, 4, 6, 8, 12, 16, 24 | 2, 4, 6, 8, 12, 16, 24 |

| 1V5            | 2, 4, 6, 8             | 2, 4, 6, 8, 12, 16     | 2, 4, 6, 8, 12, 16     |

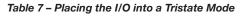

# 9. Setting the I/O into a Tristate Condition

The FPGA's I/O can be placed into a tristate condition using the TRISTATE signal on the XJLink2 connector (pin 1) provided the FPGA has been configured and its image has been designed to support this feature. The board has a 4k7 pulldown on the TRISTATE control input.

| TRISTATE (pin 1) | I/O Pins' condition |  |

|------------------|---------------------|--|

| Low              | Normal use          |  |

| High (+3V3)      | Tristate mode       |  |

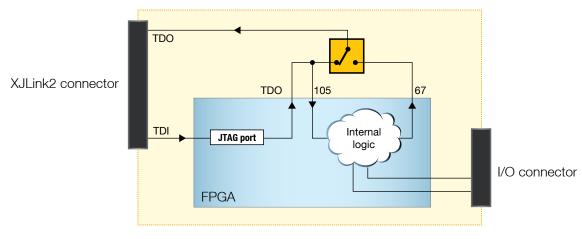

## 10. Routing TDO

The TDO signal can be returned to the XJLink2 either directly from the FPGA's JTAG port (e.g. when using the XJAccelerator for programming) or from the FPGA's internal logic (e.g. when using it as a JTAG multiplexer) as shown in Figure 7.

Figure 7 – TDO Routing

The TDO source is determined by the state of the SWITCH signal on the XJLink2 connector as described in Table 10.

| SWITCH (pin 2) | TDO source            |  |  |

|----------------|-----------------------|--|--|

| Low            | FPGA's JTAG port      |  |  |

| High (+3V3)    | FPGA's internal logic |  |  |

Table 8 – Selecting the Source of TDO

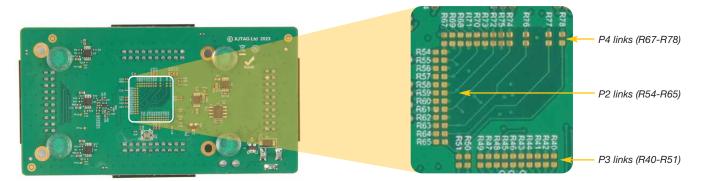

# 11. Passthrough Mode

The XJAccelerator can be configured in hardware so that some of the signals to/from the XJLink2 are routed directly to connectors P2 and P3. This can be used, for example, to utilise the XJLink2's frequency or analogue voltage measuring capabilities. Table 11 lists the locations where 0603 0  $\Omega$  links need to be placed.

**Note**: voltages applied in passthrough mode must not exceed the limits set by the FPGA because the signals are still applied to the FPGA in this mode (see the *Voltage Domains* section on page 7).

# To avoid the FPGA attempting to drive nets that are being used as passthrough, a suitable FPGA image should be used, or Disable Values or Constant pins should be set in the project.

| XJLink Pin      | P2 Pin | P2 Link | P3 Pin | P3 Link | P4 Pin | P4 Link |

|-----------------|--------|---------|--------|---------|--------|---------|

| V <sub>CC</sub> | 1      | R66     | 1      | R52     | 1      | R53     |

| 4               | 4      | R65     | 4      | R51     | 4      | R78     |

| 6               | 6      | R64     | 6      | R50     | 6      | R77     |

| 8               | 8      | R63     | 8      | R49     | 8      | R76     |

| 11              | 11     | R62     | 11     | R48     | 11     | R75     |

| 12              | 12     | R61     | 12     | R47     | 12     | R74     |

| 13              | 13     | R60     | 13     | R46     | 13     | R73     |

| 14              | 14     | R59     | 14     | R45     | 14     | R72     |

| 15              | 15     | R58     | 15     | R44     | 15     | R71     |

| 16              | 16     | R57     | 16     | R43     | 16     | R70     |

| 17              | 17     | R56     | 17     | R42     | 17     | R69     |

| 18              | 18     | R55     | 18     | R41     | 18     | R68     |

| 19              | 19     | R54     | 19     | R40     | 19     | R67     |

Table 9 – Hardware Configuration to Route Directly to the XJLink2

The links are located on the underside of the board at the positions shown in Figure 8.

Figure 8 – Locating the Links to Configure Passthrough Mode

# 12. Programming FPGA Images

The XJAccelerator uses a Xilinx<sup>®</sup> Spartan<sup>®</sup>-6 SLX9 FPGA in a 144-pin footprint. It can be programmed over the JTAG interface or from the on-board SPI flash memory.

The board's LED indicates that the FPGA has been configured. When the image is stored in the on-board flash memory, the LED should illuminate shortly after power-up; if the board is unprogrammed, the LED will remain off.

It is advisable to write the associated XJEase tests so that it automatically commences programming if an unconfigured FPGA is detected (NB: when used as a mini I/O board, no programming is needed). When written in this way, it is helpful if the code implements the following sequence:

- 1. Confirm the XJAccelerator FPGA is accessible via JTAG.

- 2. Check if the FPGA has been configured from the correct image.

- 3. If the FPGA is unprogrammed or does not contain the expected image, automatically program the on-board flash with the required image and then force the FPGA to reload from it.

XJTAG can supply the XJAccelerator together with an XJDeveloper board file and the associated XJEase files to provide this functionality.

# 13. Protection Boards

XJTAG also provides optional XJAccelerator Active Protectors which can be placed inline between the XJAccelerator and the system under test to provide additional protection to the XJAccelerator board from potentially damaging voltages. These boards are intended to be sacrificial and to fail without passing out-of-range voltages on to the XJAccelerator.

To use XJAccelerator Active Protectors, simply connect them to the 20-pin headers on the XJAccelerator board and plug in the power cable to the adjacent pin header as shown in Figure 9. It's now ready for you to connect the normal ribbon cable from the test system to the connector on the other side of the Active Protector board.

| Protection Board ratings |                                                                          |

|--------------------------|--------------------------------------------------------------------------|

| DC input voltage         | -0.5 V to 5.5 V                                                          |

| DC input current         | ±10 mA                                                                   |

| DC output current        | Pins 1, 11: +50 mA<br>-50 mA, +50 mA, including<br>power and ground pins |

| Temperature range        | +5 °C to +45 °C (operational)                                            |

| Humidity                 | < 95% (non-condensing)                                                   |

Table 10 – XJAccelerator Active Protector ratings

Figure 9 – XJAccelerator with 3 protection boards