XJAccelerator

Der XJAccelerator ist eine Mehrzweckeinheit, die in Ihr XJTAG-System integriert werden kann, um Programmierfunktionen zu erleichtern und zu beschleunigen sowie die Testabdeckung auf einem Prüfgerät (DUT) zu erweitern.

Wichtige Vorteile

Ermöglicht XJFlash-beschleunigte Flash-Programmierung

Erhöht die UUT-Testabdeckung

durch zusätzliche Schnittstellenkonnektivität

Einfache Integration

in XJTAG-Prüfsysteme

Funktionen

- Rekonfigurierbar

- FPGA-basierte Platine

- Unterstützt SPI, IIC, ICSP, SWD und andere Protokolle

- Unterstützt NOR- und NAND-Flash-Komponenten

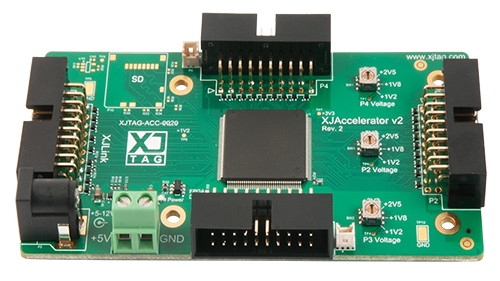

- Einfache Spannungsauswahl

- Zusätzlicher Stromanschluss für einfachere Montage in einer Prüfvorrichtung

- Stromanschlüsse für die Verwendung mit den XJAccelerator Active Protectors

JTAG gesteuerter Programmierer

Basierend auf einem Xilinx® Spartan®-6 FPGA ist die XJAccelerator-Karte hauptsächlich so konzipiert, dass sie eine vielseitige Plattform für beschleunigte Programmieranwendungen bietet. In diesem Modus ist der FPGA mit XJFlash konfiguriert, um Flash-Komponenten zu programmieren, die mit einem der drei I/O-Header verbunden sind. Die zu programmierenden Daten werden üblicherweise über JTAG in die Platine übertragen.

Die FPGA kann entweder über ihren JTAG-Port, als Teil eines Standard-XJTAG-Projekts oder über das on-Board PROM konfiguriert werden. Um die Gesamtzeit für jedes Board zu minimieren, wird der Konfigurationsstatus der FPGA bei jeder Ausführung des Projekts überprüft. Das FPGA oder das Konfigurations-PROM wird nur programmiert, wenn ein unerwarteter Status auftritt.

Vielseitige, rekonfigurierbare Lösung

Die XJAccelerator-Karte kann verwendet werden, um Standard-NOR- und NAND-Flash-Komponenten zu programmieren, sofern sie Zugriff auf alle erforderlichen Signale erhält. Weitere maßgeschneiderte Programmieroperationen sind ebenfalls möglich, sofern das Programmierprotokoll von der FPGA reproduziert werden kann.

XJTAG kann XJAccelerator-Images bereitstellen, die die folgenden Protokolle implementieren:

- SPI – Serielle Peripherieschnittstelle

- I²C (IIC)–Philips / NXP Semiconductor-Inter-IC-bus

- ICSP – Serielle Programmierung von Microchip

- SWD – Serial Wire-Debug für ARM

Wenn das von Ihnen benötigte Protokoll nicht aufgeführt ist, kontaktieren Sie uns bitte und wir werden gerne die Möglichkeit prüfen, dieses hinzuzufügen.

Das Gerät wird von einer externen 5V-Versorgung angetrieben. Die Spannungspegel für die drei I/O-Steckverbinder sind vom Benutzer von 1,2 V bis 3,3 V konfigurierbar, auswählbar per Drehschalter.

Digitale I/O-Tests

Es ist auch möglich, die Boundary-Scan-Fähigkeiten aller nicht verwendeten Signale auf den drei I/O-Headern für externe digitale I/O-Tests auf einem DUT zu verwenden.

Flexible Verbindung

Eine XJAccelerator-Platine kann in verschiedenen Konfigurationen an jeden JTAG-Controller von XJTAG angeschlossen werden und ermöglicht so eine einfache Integration in eine Vielzahl von Projekten. Sie kann entweder an einen eigenen TAP des JTAG-Controllers angeschlossen oder in Reihe mit der JTAG-Kette des Prüflings geschaltet werden.

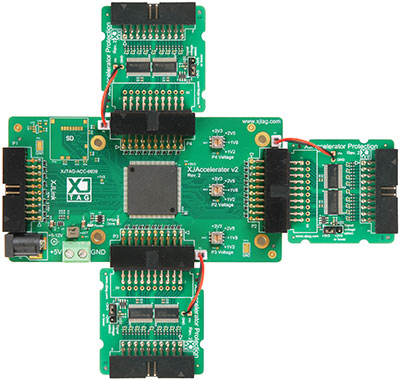

Schutzplatinen

Optionale XJAccelerator Active Protectors können zwischen dem XJAccelerator und dem zu testenden System platziert werden, um zusätzlichen Schutz für die XJAccelerator-Karte zu bieten.

Produktcode:

ACC-0020. Bitte kontaktieren Sie Ihren lokalen Händler für ein Angebot.

Vorherige Version

Dokumentation für XJAccelerator v1 ansehen.

Kompatibel mit:

| XJLink-PF40 | XJLink2 | PXI-XJLink2 | XJQuad |

| Ja (über XJA-0030/1) | Ja | Ja (über XJA-0032) | Ja |