Qu’est-ce que le JTAG et comment en tirer parti?

La technologie JTAG couvre bien plus que le débogage et la programmation

Télécharger cette page au format PDF

Vous êtes probablement familiers avec le JTAG, si vous avez déjà utilisé des outils avec cette interface. En effet, les processeurs modernes utilisent majoritairement le JTAG pour donner accès à leurs fonctions de débogage intégrées, et tous les FPGA et CPLD l’utilisent pour leur programmation.

Le JTAG n’est PAS SEULEMENT une technologie pour le débogage du code sur un processeur.

Le JTAG n’est PAS SEULEMENT une technologie pour la programmation des FPGA / CPLD.

Les outils de débogage et de programmation associés au JTAG n’utilisent qu’un aspect sous-jacent de la technologie JTAG, à savoir le protocole de communication à quatre fils.

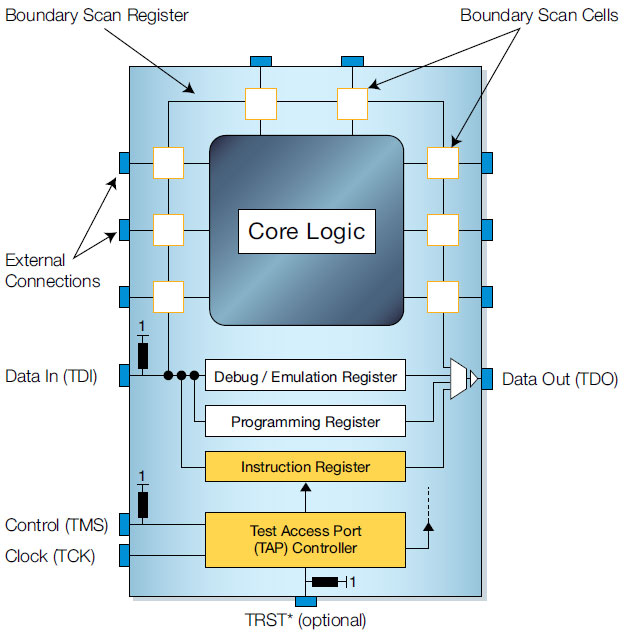

Ces quatre signaux, communément connus sous le nom de TAP (Test Access Port), font partie du standard IEEE 1149.1. Cette norme a été conçue à l’origine pour fournir une solution permettant de faciliter et d’automatiser le test des cartes électroniques sans avoir besoin de l’accès physique requis pour le test à lit de clous, ou les importants développements personnalisés nécessaires pour le test fonctionnel. Le TAP a été conçu pour interagir avec de nouveaux registres spécifiques ajoutés dans les composants afin de mettre en œuvre cette méthode de test.

Très vite, cependant, les fabricants de silicium ont compris les avantages d’utiliser le TAP pour accéder à ces registres offrant de nouvelles fonctionnalités intéressantes pour le débogage et la programmation.

Le principal registre ajouté spécifiquement pour le test JTAG s’appelle le Registre Boundary Scan (BSR). Comme son nom l’indique, les bits (ou cellules) individuels de ce registre sont implantés à la périphérie (Boundary) du composant, entre son noyau fonctionnel et les broches par lesquelles il est connecté à une carte. C’est pourquoi, très souvent, le test JTAG est aussi appelé « Boundary Scan ».

Comment le JTAG / Boundary Scan est utilisé pour tester une carte

Les cellules Boundary Scan (voir la figure ci-dessus) peuvent fonctionner en deux modes. Dans le mode « fonctionnel », ces cellules n’ont aucun effet sur le fonctionnement du composant ; et les cellules sont placées dans ce mode lorsque la carte fonctionne normalement. Dans le mode « test » au contraire, les cellules isolent le noyau fonctionnel du composant des broches externes. En mettant les cellules Boundary Scan en mode test, celles-ci peuvent être utilisées pour contrôler les valeurs envoyées par un composant compatible JTAG sur un ensemble de connexions, ou pour surveiller l’état de ces connexions.

La possibilité d’isoler le contrôle des broches de la fonctionnalité du composant JTAG rend le test Boundary Scan beaucoup plus simple à mettre en œuvre que le test fonctionnel traditionnel, car le composant ne doit pas être configuré ou démarré pour pouvoir utiliser ces broches. En fournissant un mécanisme pour contrôler et surveiller tous les signaux activés sur un composant à partir d’un contrôleur TAP à quatre broches, le JTAG réduit considérablement l’accès physique nécessaire pour tester une carte.

Il existe deux façons principales pour utiliser cette fonctionnalité du Boundary Scan pour tester une carte électronique. La première façon, le test de connexion (voir le titre/paragraphe suivant) fournit une bonne couverture de test, en particulier pour la détection des courts-circuits. Il est basé uniquement sur les fonctionnalités du composant JTAG, les interconnexions de la carte, et – dans le cas de XJTAG – également sur le fonctionnement des composants logiques de la carte (p.ex. portes logiques, buffers). La deuxième façon étend cette couverture en utilisant les composants JTAG sur une carte pour communiquer avec des composants non-JTAG, tels que les RAM DDR ou la mémoire flash.

Qu'est-ce qu'un test de connexion JTAG?

Un test de connexion JTAG vérifie sur une carte électronique que les connexions autour des composants JTAG sont telles qu’elles ont été spécifiées lors de la conception.

Lorsque deux broches avec contrôle JTAG doivent être connectées, le test s’assurera que l’une des broches puisse être contrôlée par l’autre. Par contre, si les broches avec contrôle JTAG ne doivent pas être connectées, elles sont testées pour détecter des défauts potentiels de court-circuit en pilotant une broche et en vérifiant que ces valeurs forcées ne sont pas lues sur les autres.

Les résistances de rappel (pull-up/down) manquantes et les pannes de « collage » peuvent également être identifiées par un test de connexion, ainsi que les défaillances qui affectent des composants logiques dont le comportement peut être décrit dans une table de vérité.

XJTAG génère automatiquement les vecteurs nécessaires pour exécuter un test de connexion basé sur la liste d’interconnexions (netlist) de la carte et sur les informations sur les composants compatibles JTAG.

Qu'en est-il des composants non compatibles JTAG?

Alors que les principaux composants, tels que les processeurs et les FPGA, sont normalement compatibles avec JTAG, il y a beaucoup d’autres composants sur une carte électronique qui ne le sont pas. Les DDR, SDRAM, SRAM, mémoires flash, contrôleurs Ethernet, les capteurs de température SPI et I2C, les horloges en temps réel, et les convertisseurs A/N et N/A ne sont que quelques exemples de ces composants.

Le test de connexion fournira une excellente couverture de test pour les courts-circuits sur les réseaux reliant ces composants non-JTAG à des composants compatibles JTAG ; néanmoins il n’est pas en mesure de vérifier les défauts de circuits ouverts soit sur le composant JTAG ou soit sur le composant non-JTAG.

Afin d’étendre la couverture aux circuits ouverts, il est nécessaire de communiquer avec le périphérique non-JTAG à partir du Boundary Scan dans le composant JTAG. Si la communication entre les deux peut être vérifiée, il n’y a pas de circuit ouvert. Ce type de test peut être très simple (p. ex. allumer une LED et demander à un opérateur de confirmer si elle a été activée) ou plus complexe (p.ex. écrire des données dans la mémoire d’une RAM et les relire).

Faut-il beaucoup de travail pour développer un test JTAG?

En utilisant les bibliothèques de composants standards non-JTAG fournies par XJTAG, vous pouvez obtenir immédiatement un ensemble de tests prêts à être exécutés sur votre carte sans développement de code. La bibliothèque contient des modèles pour tous les types de composants non-JTAG, depuis des résistances et des buffers simples jusqu’à des mémoires complexes tels que des DDR3. Étant donné que le Boundary Scan déconnecte sur les composants JTAG le contrôle des broches de leur fonctionnalité réelle, le même modèle peut être utilisé quel que soit le composant JTAG qui contrôle un composant particulier.

La plupart des circuits imprimés contiennent déjà des connecteurs JTAG pour la programmation ou le débogage, donc qu’il n’y a pas d’exigences supplémentaires de conception pour utiliser cette technologie.

Où puis-je obtenir des informations sur le support JTAG pour mes composants?

Pour exécuter des tests basés sur le Boundary Scan, il est nécessaire d’avoir des informations sur la mise en œuvre du JTAG sur les composants compatibles de la carte. Ces informations sont contenues dans les fichiers BSDL (Boundary Scan Description Language) du composant. Le fournisseur de silicium doit mettre à disposition les fichiers BSDL pour assurer qu’un composant est conforme à la norme IEEE 1149.1.

Le test JTAG est-il exclusivement utilisé dans la production?

Pas du tout ! L’un des principaux avantages du Boundary Scan est que le seul matériel requis pour le test est un contrôleur JTAG. D’autres technologies de test utilisées dans la production, tels que la sonde mobile (Flying Probe), l’inspection optique/à Rayons X automatiques ou le test à lit de clous ont besoin d’équipements de tests spécialisés qui ne sont généralement pas disponibles sur le banc de test des ingénieurs.

Pendant la mise au point de la carte, le Boundary Scan peut éliminer les incertitudes : les concepteurs peuvent tester leurs prototypes et trouver les défauts de fabrication avant les tests du système, et même avant que le firmware ne soit terminé. Des systèmes de test JTAG développés à cette phase initiale du cycle de vie du produit peuvent être facilement réutilisés et étendus ensuite pour la production.

Trois lettres simples – BGA

Un nombre croissant de composants sont fournis en boîtier BGA (Ball Grid Array). Chaque composant BGA sur une carte impose des restrictions sévères sur les tests qui peuvent être effectués par des testeurs traditionnels, tels que lit de clous ou sondes mobiles.

À l’aide d’une interface simple à quatre broches, le JTAG / Boundary Scan permet de contrôler et analyser les signaux sur les composants compatibles, sans aucun accès physique direct.

Trois autres lettres – NRE

Les coûts d’ingénierie non récurrents (NRE) liés au développement des bancs de test peuvent s’avérer prohibitifs. Dans de nombreux cas, le test JTAG / Boundary Scan peut supprimer la nécessité d’un tel outillage, dans d’autres cas, l‘outillage peut être considérablement simplifié, ce qui entraîne des économies considérables.

Temps d'exécution de test plus courts

Dans le cas des cartes à faible volume de production, il a toujours été difficile de justifier le coût du développement des bancs de test. Dans ce cas-là, les testeurs à sondes mobiles offrent une alternative viable, mais avec cette technologie le temps d’exécution du cycle de test a tendance à être très long. Le test JTAG / Boundary Scan offre un temps d’exécution de tests court, sans besoin de banc de test coûteux.

Réduction des coûts de développement des tests

Étant donné que les différents processeurs et FPGA interagissent avec les composants de différentes façons, le test fonctionnel traditionnel nécessite un développement personnalisé coûteux pour chaque carte. Le JTAG / Boundary Scan réduit considérablement ces coûts de développement, en fournissant une interface simplifiée pour contrôler les broches d’E/S utilisées pour interagir avec les différents composants. Cette interface standard, qui est identique pour tous les périphériques compatibles JTAG, signifie qu’un ensemble générique de modèles de test peut être utilisé et réutilisé lors du développement des systèmes de test.

Un seul outil pour tester et programmer

Le JTAG est déjà souvent utilisé comme une des étapes de la production, la programmation. En utilisant le JTAG également pour le test Boundary Scan, il est possible de réduire le nombre d’étapes et de défauts dus à la manipulation dans le processus de production.

Tests de niveau production réalisés pour les prototypes électroniques

Les technologies de test traditionnelles requièrent un équipement très élaboré et coûteux. Le seul équipement de test requis pour les tests JTAG / Boundary Scan est une sonde JTAG. Le contrôleur XJLink2 de XJTAG est de taille similaire à celle d’une souris pour PC.

Diagnostic de défaut rapide et précis

Contrairement au test fonctionnel, le JTAG / Boundary Scan fournit des informations très précises sur les défauts détectés sur la carte, ce qui facilite une réparation rapide. XJTAG fournit également la possibilité de visualiser à la fois l’emplacement physique du défaut sur le routage de la carte, et la zone de problèmes sur le schéma électronique.

Récupérez les cartes hors d'usage où le test fonctionnel ne serait pas suffisant

Les tests JTAG Boundary Scan peuvent être exécutés sur n’importe quelle carte avec une interface JTAG fonctionnelle. Les tests fonctionnels traditionnels ne peuvent pas être exécutés si la carte ne démarre pas. Les défauts simples sur les périphériques clés, tels que la RAM ou les horloges, empêcheraient les tests fonctionnels de fournir des informations de diagnostic, alors qu’ils seraient facilement identifiés à l’aide du JTAG.

Autres ressources

Tutoriel général de JTAG

Découvrez ce que JTAG peut faire

Guide technique de JTAG (en anglais)

Un regard de bas niveau à la façon dont JTAG est mis en œuvre

Recommandations pour la Conception en Vue du Test (DFT)

Recommandations pour améliorer la testabilité des cartes PCB

Test JTAG avec XJTAG (en anglais)

Comment XJTAG étend les possibilités de JTAG

- La technologie JTAG couvre bien plus que le débogage et la programmation

- Comment le JTAG / Boundary Scan est utilisé pour tester une carte

- Qu'est-ce qu'un test de connexion JTAG?

- Qu'en est-il des composants non compatibles JTAG?

- Faut-il beaucoup de travail pour développer un test JTAG?

- Où puis-je obtenir des informations sur le support JTAG pour mes composants?

- Le test JTAG est-il exclusivement utilisé dans la production?

- Trois lettres simples – BGA

- Trois autres lettres – NRE

- Temps d'exécution de test plus courts

- Réduction des coûts de développement des tests

- Un seul outil pour tester et programmer

- Tests de niveau production réalisés pour les prototypes électroniques

- Diagnostic de défaut rapide et précis

- Récupérez les cartes hors d'usage où le test fonctionnel ne serait pas suffisant

Etes-vous prêt à commencer?

Voir XJTAG à l’oeuvre

Notre équipe d’experts vous montrera comment diagnostiquer les défauts sur votre carte électronique, comment réduire le temps de développement des tests et le temps de réparation grâce aux outils XJTAG.

Une question? Contactez-nous!

Envoyez-nous un message et un de nos spécialistes vous répondra dans les plus brefs délais.

Recevez une configuration de test gratuite pour une de vos cartes

Aucune obligation d’achat.