JTAGとは何ですか、またどのように使用できますか?

JTAGはデバッグとプログラミング以外にも活用されます

JTAGインターフェースを備えたツールを使用したことがあり、それに精通しているかもしれません。プロセッサは多くの場合、JTAGデバッグ/エミュレーション機能を提供しますし、すべてのFPGAおよびCPLDはJTAGを使用したプログラミング機能を提供します。

しかしながら、

JTAGは、プロセッサのデバッグ/エミュレーションだけに利用される技術ではありません。JTAGは、FPGA / CPLDのプログラミングだけに利用される技術ではありません。

JTAGによるデバッグやプログラミングは、JTAG技術の中から4本のJTAG信号接続からなる通信プロトコルのみを、単に利用しているに過ぎません。

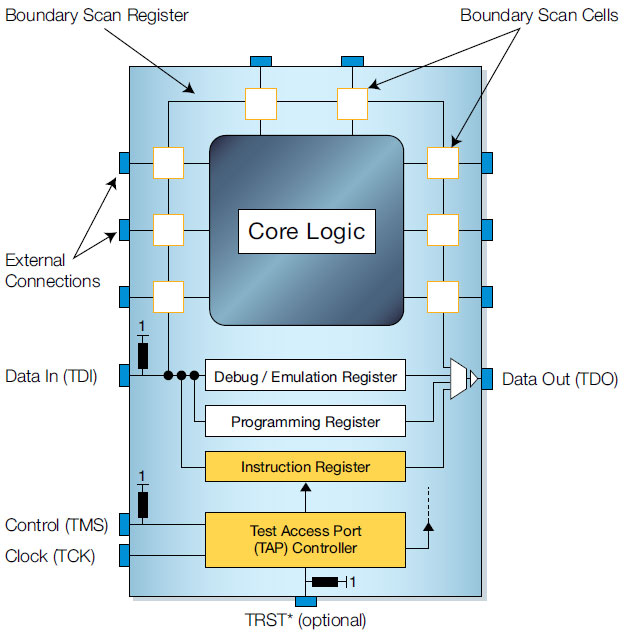

これら4つのJTAG信号は、Test Access PortまたはTAPと呼ばれ、IEEE Std 1149.1の一部です。この規格は、プローブ治具(ネイルベッド治具)の物理的アクセスを削減して、機能テストのカスタム開発を軽減する、プリント回路板アセンブリ(PCBA)のテスト技術を提供するために開発されました。そしてTAPは、このテストを実装するためにデバイスに新しく追加されたレジスタと対話するように設計されました。

また一方、TAPを使用してデバッグやプログラミング機能を提供するレジスタにアクセスできることの利点が認識され、シリコンメーカーによるデバッグやプログラミングへの採用が一気に進みました。。

JTAGテスト専用にデバイスに追加されるメインレジスタは、バウンダリスキャンレジスタ(BSR)と呼ばれます。その名前が示すように、このレジスタの個々のビットまたはセルは、デバイスの機能コアとボードに接続されるピンまたはボールの間の境界にあります。JTAGテストは、しばしばバウンダリスキャンと呼ばれます。

JTAG /バウンダリスキャンを使用してボードをテストする方法

バウンダリスキャンセル(上記参照)は2つのモードで動作します。機能モードでは、デバイスの動作には影響しません。これは、ボードが通常動作しているときのモードです。テストモードでは、デバイスの機能コアをピンから切り離します。バウンダリスキャンセルをテストモードにすると、JTAGデバイスからネット上に駆動される値を制御したり、そのネットの値を監視したりできます。

JTAGデバイスの機能からピンの制御を切り離すことで、バウンダリスキャンテストの開発は従来の機能テストよりも大幅に簡単になります。デバイスのコンフィグレーションやブートを行う必要がないためです。JTAGは、4ピンTAPを介してJTAGデバイスで有効なすべての信号を制御および監視するメカニズムを提供することにより、ボードのテストに必要となる物理アクセスを大幅に削減します。

このバウンダリスキャン機能を使用してボードをテストするには、主に2つの方法があります。まず接続テスト(次章を参照)は、特に短絡障害に良好なテストカバレッジを提供します。これは、純粋にJTAGデバイスの機能として基板上の接続とネット、加えてXJTAGの場合はボード上のロジック機能をサポートします。2つ目の方法は、ボード上のJTAG対応デバイスを使用して、DDR RAMやフラッシュメモリなどの非JTAG周辺デバイスと通信することにより、カバレッジを拡張します。

JTAG接続テストとは何ですか?

JTAG接続テストは、ボード上のJTAG対応デバイス周りの接続が設計と同じであることを確認します。

2つのJTAG対応ピンが接続されている場合、テストは1つのピンが他のピンによって制御できることを確認します。JTAG対応ピンが接続されない場合は、そのピンを駆動し、その値が他のピンで読み取られないことを確認することにより、短絡障害をテストします。

プル抵抗の欠落やスタックの障害、動作を真理値表に記載できる論理デバイスに関連する障害も、接続テストで検出されます。

XJTAGは、ボードのネットリストとJTAGデバイスの情報に基づいて、接続テストの実行に必要なテストベクターを自動生成します。

JTAGが有効になっていないデバイスはどうですか?

プロセッサやFPGAなどメインのデバイスは通常JTAG対応ですが、もちろんそうでない多くのデバイスもあります。DDR、SDRAM、SRAM、フラッシュメモリ、MDIO制御イーサネットPHY、SPIおよびI2C温度センサー、リアルタイムクロック、ADCおよびDACは、このようなデバイスの一例です。

接続テストは、これらの非JTAGデバイスのJTAG対応デバイスにリンクするネット上の短絡障害に優れたカバレッジを提供します。ただし、JTAGデバイスまたは非JTAGデバイスのいずれかのオープンエラーをチェックすることはできません。

そのようなオープンエラーのカバレッジを追加するには、JTAGデバイスのバウンダリスキャン機能を用いて、周辺デバイスと通信する必要があります。通信が検証できるなら、断線障害はありません。このテストの非常に単純な例は、LEDを点灯させて、オペレーターがアクティブになったことを確認することです。もう少し高度な例は、RAMのメモリアレイにデータを書き込み、それを読み返すことによる検証です。

XJTAGテストシステムの作成は難しくない?

簡単です。テストプログラムを実装する必要はありません。XJTAGが標準提供する非JTAGコンポーネント用のライブラリを用いて、基板のテストセットを用意して実行することができます。ライブラリファイルには、単純な抵抗やバッファから、DDR3などの複雑なメモリデバイスまで、すべてのタイプの非JTAGデバイスのモデルが含まれています。バウンダリスキャンはJTAGデバイスのピンの制御をその中核となる機能から切り離すので、周辺機器を制御するJTAGデバイスに関係なく同じライブラリファイルを使用できます。

ほとんどのボードには、プログラミングまたはデバッグ用のJTAGヘッダーがすでに含まれているので、追加の設計要件はありません。

デバイスのJTAGに関する情報はどこで入手できる?

バウンダリスキャンテストを実行するには、基板上のJTAGデバイスのJTAGの実装に関する情報が必要です。この情報は、これらのデバイスのBSDL(Boundary Scan Description Language)ファイルから取得されます。IEEE Std 1149.1に準拠するデバイスには、シリコンベンダーからBSDLファイル が提供されます。

JTAGテストは製造工程以外でも使用されている?

はい。バウンダリスキャンテストの主な利点の1つは、必要なテストハードウェアがJTAGコントローラーのみであることです。フライングプローブ、自動光学/ X線検査、プローブ治具(ネイルベッド治具)などの他の生産テスト技術には、エンジニアサイドでは使用できないような特殊なテスト機器が必要です。

基板の立ち上げ時にバウンダリスキャンを使用して、早期段階から不確実性を排除することができます。ハードウェアエンジニアは、システムテストの前、さらにはファームウェアが用意される前に、プロトタイプボードの製造欠陥をテストできます。そして製品ライフサイクルの初期段階で開発されたテストシステムは、製造検査時にも簡単に再利用できます。

BGAという単純な3文字

BGA(Ball Grid Array)パッケージは増加の一方です。基板上の各BGAデバイスは、従来のプローブ治具(ネイルベッド治具)またはフライングプローブマシンを使用して実行できるテストに厳しい制限を課しています。

JTAG /バウンダリスキャンはシンプルな4ピン接続を使用して、物理的にアクセスすることなくJTAGデバイス上の信号を制御および監視できます。

さらに3文字– NRE

近年、テストフィクスチャを構築するためのNRE(non-recurring engineering)コストは非常に高くなる傾向ですが、多くの場合、JTAG /バウンダリスキャンを使用すると、このようなフィクスチャが不要になります。また、フィクスチャを大幅に簡素化してコストを飛躍的に削減します。

テスト時間をもっと速く

生産量が少ないボードの場合、テストフィクスチャ開発のコストを正当化することは常に困難です。これらの場合、1つの選択肢はフライングプローブテストです。ただし、この技術ではテストのサイクル時間が長くなる傾向があります。JTAG /バウンダリスキャンテストは、高価なフィクスチャを必要とせずにテスト時間を短縮します。

テスト開発をもっと安く

さまざまなプロセッサ/ FPGAが、さまざまな方法で周辺機器と対話するので、従来の機能テストでは、コストのかかるカスタム開発が基板ごとに必要です。JTAG /バウンダリスキャンは、周辺機器とのやり取りに使用されるIOピンを制御するためのシンプルなインターフェースを提供するため、このような開発コストを大幅に削減します。すべてのJTAG対応デバイスで同じこの標準インターフェースは、テストシステムの構築時にテストモデルの汎用セットを使用および再利用できることを意味します。

テストとプログラミングを1つのツールで

JTAGは、製造過程の1ステップとして、既にプログラミングで使用されていることがよくあります。このJTAGをバウンダリスキャンテストにも使用することにより、製造プロセスのステップ数と処理操作を減らすことができます。

プロトタイプ基板のテストやデバッグに好都合

従来のテスト技術は、非常に大きくて高価な機器が必要です。JTAG /バウンダリスキャンテストに必要なテスト機器は、JTAGコントローラーのみです。XJTAGのXJLink2コントローラーのサイズは、PCのマウスと同じ程度です。

わかりやすい障害診断機能

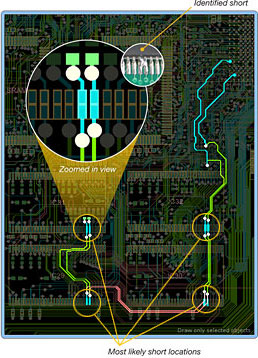

JTAG /バウンダリスキャンは、機能テストとは異なり、高精度の障害情報を提供して迅速な修復を支援します。XJTAGには、ボードのレイアウト上の障害の物理的な位置と、回路図上で障害が存在する回路領域の論理設計の両方を表示する機能があります。

機能テストが動かない基板も回復させる

JTAG /バウンダリスキャンテストは、JTAGインターフェースさえ動作すれば、どの基板でも実行できます。従来の機能テストは、基板が起動しないと実行できません。RAMやクロックなどの主要な周辺機器の単純な障害は、JTAGを使用して検出されますが、機能テストでは診断情報を提供できません。