¿Qué es JTAG y cómo puedo usarlo?

JTAG es más que depuración y programación

Puede que esté familiarizado con JTAG porque ha usado herramientas con interfaz JTAG. Los procesadores usan a menudo JTAG para acceder a sus funciones de depuración/emulación y todas las FPGAs y CPLDs usan JTAG para dar acceso a sus funciones de programación.

JTAG no es solamente una tecnología para la depuración/emulación de procesadores. JTAG no es solamente una tecnología para la programación de FPGAs/CPLDs.

Las herramientas de depuración y programación comúnmente asociadas a JTAG solo hacen uso de un aspecto de tecnología JTAG – el protocolo de comunicación de cuatro hilos.

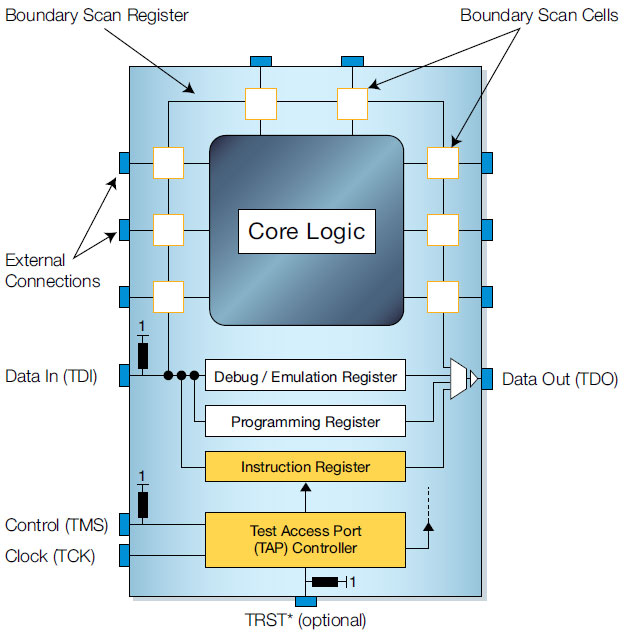

Estas cuatro señales, conocidas colectivamente como Test Access Port o TAP, forman parte del estándar IEEE 1149.1. Este estándar fue desarrollado como una tecnología para facilitar y automatizar el test de circuitos impresos (PCBA, del inglés Printed Circuit Board Assemblies) sin la necesidad del nivel de acceso físico requerido por los tests de cama de pinchos (bed-of-nails) o la complejidad y personalización necesaria del desarrollo de pruebas funcionales. El puerto TAP fue diseñado para interactuar con nuevos registros que fueron añadidos a componentes para implementar este método de testeo.

Sin embargo, los fabricantes de silicio rápidamente vieron los beneficios de usar el TAP para acceder a estos registros, ofreciendo otras funcionalidades como la depuración y la programación.

El registro principal específico añadido a un componente para el testeo JTAG se llama Boundary Scan Register (BSR). Como su propio nombre indica, los bits (o células) individuales de este registro están en el borde del componente, entre su núcleo funcional y los pines o bolas mediante el cual está conectado a la placa – muy a menudo el testeo JTAG es referido como boundary scan.

Como XJTAG usa JTAG / Boundary Scan para testear una tarjeta

Las celdas de boundary scan (ver la figura anterior) pueden funcionar en dos modos. En modo “funcional” estas celdas no tienen ningún efecto sobre el funcionamiento del componente; las celdas se colocan en este modo cuando la placa funciona normalmente. En el modo “test”, por el contrario, las células aíslan el núcleo funcional del componente de los pines externos. Al poner las celdas de boundary scan en modo test, estas se pueden utilizar para verificar los valores enviados desde un componente compatible con JTAG a un conjunto de conexiones, así como para monitorear el estado de dichas conexiones.

La posibilidad de aislar el control de los pines con respecto de la funcionalidad del componente hace que el desarrollo de los tests boundary scan sea mucho más sencillo que un test funcional tradicional, ya que el componente no necesita ser configurado o iniciado para habilitar dichos pines. Al proporcionar un mecanismo para controlar y monitorear todas las señales habilitadas en un componente desde un controlador TAP de cuatro pines, los tests JTAG reducen significativamente el acceso físico requerido para testear una placa.

Hay dos formas principales de utilizar esta funcionalidad boundary scan para testear una tarjeta electrónica. La primera de ellas, el test de conexiones (consulte el siguiente apartado), proporciona una buena cobertura de test, especialmente para la detección de cortocircuitos. Se basa específicamente en las capacidades de los componentes JTAG, las conexiones y nets en la placa y, en el caso de XJTAG, también en el funcionamiento de los dispositivos lógicos existentes (por ejemplo, puertas lógicas). La segunda amplía la cobertura del test mediante el uso de componentes JTAG para comunicarse con otros componentes periféricos que no están habilitados para JTAG, como DDR RAM o memorias flash.

¿Qué es el test avanzado de conexión de XJTAG?

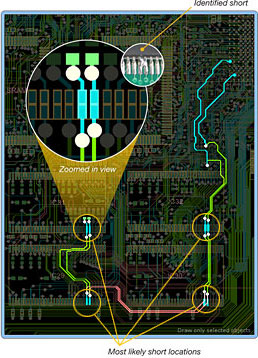

El test de conexión JTAG verifica que las conexiones alrededor de los componentes JTAG respetan las especificadas en el diseño.

Cuando dos pines habilitados para JTAG deben estar conectados, el test comprueba que cada pin puede ser controlado por el otro. Por el contrario, si los pines controlados por JTAG no se van a conectar, se testean para detectar cortocircuitos activando un pin y verificando que estos valores forzados no se leen en los otros pines. También se puede detectar la falta de resistencias pull-up/down y fallos de ‘stuck-at’.

El test de conexión avanzado de XJTAG también identifica automáticamente otros posibles problemas, como cortocircuitos en resistencias en serie o fallos en componentes lógicos cuyo comportamiento puede ser descrito en una tabla de la verdad.

¿Qué pasa con los componentes no habilitados para JTAG?

Mientras que los componentes principales, tales como procesadores y FPGA, están normalmente habilitados para JTAG, habrá muchos otros componentes en cada diseño que no lo estén. DDR, SDRAM, SRAM, Flash, MDIO controlando la capa física Ethernet (PHY), sensores de temperatura SPI e I2C, clocks en tiempo real (RTC), ADCs y DACs son sólo algunos ejemplos de tales componentes.

El test de conexión proporcionará una excelente cobertura para la detección de cortocircuitos en las nets que conectan estos componentes no JTAG a componentes habilitados para JTAG. Sin embargo, este test no puede detectar si hay pistas abiertas en los componentes JTAG y no JTAG.

Para extender la cobertura de test a circuitos abiertos, es necesario comunicarse con el dispositivo periférico no JTAG desde las celdas Boundary Scan en el componente JTAG. Si se puede verificar la comunicación entre los dos, entonces no hay circuito abierto. Este tipo de prueba puede ser muy sencilla (por ejemplo, encender un LED y pedirle a un operador que confirme si se ha activado) o más compleja (por ejemplo, escribir datos en el array de una memoria RAM y leerlos de vuelta).

¿Requiere mucho trabajo crear un sistema de test JTAG?

Usando la biblioteca instalada con el software XJTAG para componentes estándar no JTAG, están disponibles un conjunto de tests que funcionan inmediatamente en su placa, sin necesidad de escribir ningún código. La biblioteca XJTAG contiene modelos para todo tipo de componentes no JTAG, desde simples resistencias y buffers hasta componentes más complejos como memorias DDR3. Dado que Boundary Scan desconecta el control de pines en los componentes JTAG de su funcionalidad real, se puede usar el mismo modelo independientemente del componente JTAG que controla un periférico en particular.

La mayoría de las tarjetas ya contienen headers JTAG para programar o depurar, de modo que no hay requisitos de diseño adicionales.

¿Dónde puedo obtener información sobre la implementación de JTAG en mis componentes?

Para ejecutar cualquier test basado en Boundary Scan, es necesario tener cierta información sobre la implementación de JTAG en los componentes habilitados de la placa. Esta información está contenida en los archivos BSDL (Boundary Scan Description Language) de estos componentes. El proveedor de silicio debe hacer que los archivos BSDL estén disponibles para garantizar que un componente cumple el estándar IEEE 1149.1.

¿Los tests JTAG se utilizan exclusivamente en producción?

¡Para nada! Una de las principales ventajas de los tests boundary scan es que el único hardware necesario es un controlador JTAG. Otras tecnologías de test utilizadas en producción, como los sistemas Flying Probe, la Inspección Óptica Automática (AOI) / Rayos-X (AXI), o las Camas de Pinchos, requieren de equipos de test especializados que no estarán disponibles en el escritorio de un ingeniero.

El uso del boundary scan durante la fase de prototipado puede eliminar incertidumbres. De hecho, los ingenieros de hardware pueden testear prototipos para detectar defectos de fabricación antes de testear el sistema, e incluso antes de que el firmware esté disponible. Los sistemas de test JTAG desarrollados en esta fase temprana del ciclo de vida del producto pueden reutilizarse fácilmente y posteriormente ser usados para la producción.

Ocho razones por las que debería usar XJTAG para testear sus placas

Tres simples letras – BGA

Cada vez más componentes se suministran en paquetes BGA (Ball Grid Array). Cada componente BGA en una placa impone severas restricciones respecto de los tests que se pueden realizar con los equipos tradicionales, como las Camas de Pinchos o las máquinas automáticas Flying Probe.

Usando una interfaz simple de cuatro pines, el test JTAG / boundary scan permite controlar y monitorear señales en componentes habilitados para JTAG sin ningún acceso físico directo.

Tres letras más – NRE

Los costes de ingeniería no recurrentes (NRE) asociados al desarrollo de bancos de test pueden ser prohibitivamente altos. En muchos casos, el uso de JTAG / Boundary scan puede eliminar la necesidad de tales equipos, mientras que en otros casos, el banco de test se puede simplificar en gran medida, lo que conlleva ahorros significativos.

Tiempos de testeo más cortos

Para tarjetas con bajos volumenes de producción, siempre ha sido difícil justificar el coste de desarrollar bancos de prueba. En estos casos, los testers flying probe ofrecen una alternativa viable; sin embargo con esta tecnología el tiempo de ejecución del ciclo de test tiende a ser muy elevado. El test JTAG / Boundary Scan ofrece tiempos de ejecución de test reducidos sin la necesidad de un costoso banco de pruebas .

Menores costes de desarrollo de tests

Debido a que los diferentes procesadores y FPGA interactúan con los periféricos de diferentes modos, el test funcional tradicional requiere un costoso desarrollo personalizado para cada placa. El test JTAG / Boundary Scan reduce significativamente estos costes de desarrollo, ya que proporciona una interfaz simplificada para controlar los pines de I/O utilizados para interactuar con los diversos componentes.

Esta interfaz estándar, que es común para todos los componentes de la cadena JTAG, implica que al desarrollar sistemas de test se puede utilizar y reutilizar conjuntos genéricos de modelos de test.

Una herramienta para testear y programar

El puerto JTAG a menudo ya se utiliza para un paso en la producción: la programación. Utilizar también JTAG para el test Boundary Scan permite reducir el número de pasos y operaciones de manipulación en el proceso de producción.

Tests del nivel de producción al alcance de ingenieros para la fase de prototipado

Las tecnologías de test tradicionales requieren equipos muy grandes y costosos. El único equipo necesario para el test JTAG / Boundary Scan es un controlador JTAG; el controlador XJLink2 de XJTAG es de tamaño similar a un ratón de PC.

Excelente diagnóstico de fallos

A diferencia de los Tests Funcionales, el test JTAG / Boundary Scan proporciona información muy precisa sobre los fallos detectados en la placa, lo que facilita una rápida reparación. XJTAG también permite ver tanto la ubicación física de un fallo en el layout de la placa como el diseño lógico de la zona del circuito donde se encuentra el fallo en el esquemático.

Recuperación de tarjetas defectuosas en las que los tests funcionales no funcionarían

Los tests Boundary Scan de XJTAG se pueden ejecutar en cualquier tarjeta con interfaz JTAG. Los tests funcionales tradicionales no se pueden ejecutar si el firmware de la placa no es capaz de inicializarse. Fallos simples en los periféricos, tales como la RAM o los clocks, evitarían que los tests funcionales proporcionaran información de diagnóstico, mientras que a través de JTAG se detectarían fácilmente.

Otros recursos

Guía de alto nivel para JTAG

Ver lo que JTAG puede hacer

Guía técnica de JTAG

Una mirada de bajo nivel en cómo se implementa JTAG

Directrices para el diseño para las pruebas (DFT)

Sugerencias para mejorar el test de placas PCB

Tests JTAG usando XJTAG

Cómo XJTAG amplía las posibilidades de JTAG

¿Listo para empezar?

¡Ver XJTAG en acción!

Nuestros expertos estarán encantados de mostrarle cómo las herramientas XJTAG pueden ayudarle a diagnosticar fallos en su placa, así como a reducir el tiempo de desarrollo de tests y reparaciones.

![]()

¿Tiene preguntas? ¡Contáctenos!

Envíenos un mensaje y uno de nuestros especialistas en tests se pondrá en contacto con usted lo antes posible.