Cos’è il JTAG e come posso utilizzarlo?

JTAG è più che debug e programmazione

Scarica questa pagina in formato PDF

Potresti avere familiarità con il JTAG perché hai già utilizzato strumenti con questa interfaccia. I processori spesso utilizzano il JTAG per fornire l’accesso alle loro funzioni di debug/emulazione, e tutte le FPGA e CPLD utilizzano il JTAG per accedere alle proprie funzioni di programmazione.

JTAG NON è SOLO una tecnologia per il debug/emulazione di processori.

JTAG NON è SOLO una tecnologia per la programmazione delle FPGA/CPLD.

Gli strumenti di debug e di programmazione comunemente associati al JTAG utilizzano solo un aspetto della tecnologia che vi è alla base – il protocollo di comunicazione JTAG a quattro fili.

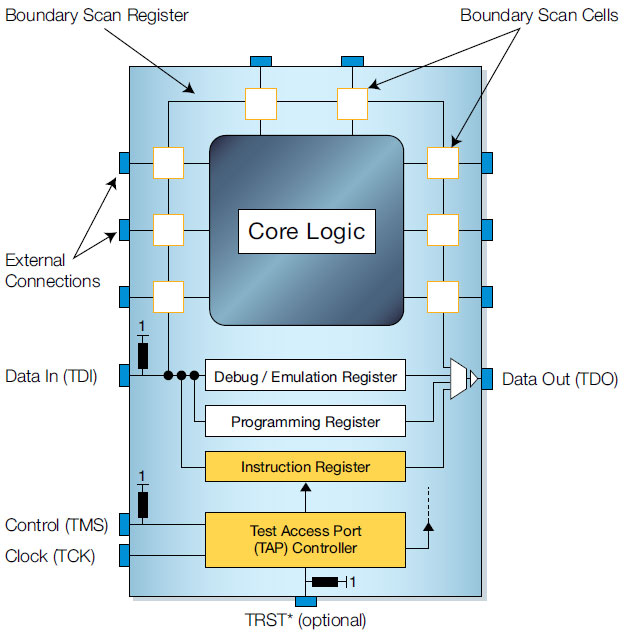

Questi quattro segnali, comunemente conosciuti come Test Access Port (o TAP), fanno parte dello standard IEEE 1149.1. Questo standard è stato sviluppato per fornire una tecnologia utile a testare quelle schede elettroniche anche senza un livello di accesso fisico necessario per il test con letto d’aghi, o senza uno sviluppo ad-hoc necessario per il test funzionale. Il TAP è stato progettato per interagire con nuovi registri aggiunti nei componenti al fine di implementare questa metodologia di test.

Molto rapidamente, tuttavia, i produttori di silicio hanno riconosciuto i vantaggi di utilizzare il TAP per accedere ai registri che offrono altre funzionalità, come il debug e la programmazione.

Il registro principale aggiunto a un dispositivo specificamente per il test JTAG viene chiamato Boundary Scan Register (BSR). Come il suo nome suggerisce, i singoli bit (o celle) di questo registro sono implementati in prossimità della periferia (boundary) del componente, tra il suo core e i pin (o balls) esterni con cui esso è collegato alla scheda – molto spesso il test JTAG è definito “Boundary Scan”.

Come il JTAG / boundary scan è utilizzato per testare una scheda

Le celle boundary scan (vedi figura in alto) possono operare in due modalità diverse. Nella loro modalità “funzionale”, le celle non hanno alcun effetto sul funzionamento del componente; questa è la modalità nella quale le celle sono configurate quando la scheda lavora normalmente. Nella loro modalità “test”, invece, le celle isolano il core del componente dai suoi pin esterni. Configurando, quindi, le celle nella modalità “test”, queste possono essere utilizzate per controllare i valori che saranno forzati su una net da un componente JTAG, oppure per monitorare lo stato di quella net.

La possibilità di isolare il controllo dei pin dalla funzionalità del componente abilitato JTAG rende il test boundary scan decisamente più semplice di un tradizionale test funzionale, in quanto non è richiesta nessuna configurazione del componente per poter abilitare i pin. Mettendo a disposizione un meccanismo con il quale è possibile monitorare tramite un TAP a 4 pin tutti i segnali abilitati su una scheda, il JTAG riduce significativamente l’accesso fisico richiesto per testare una scheda.

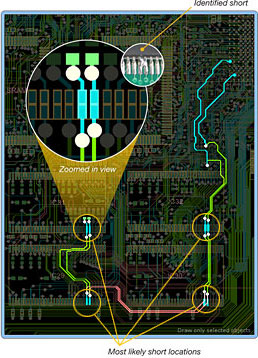

Ci sono due diversi modi in cui è possibile utilizzare le proprietà del boundary scan per testare una scheda. Il primo, il test di connessione (vedi il prossimo paragrafo), fornisce una buona copertura di test, in particolare per il rilevamento di eventuali cortocircuiti presenti sulla scheda. Esso si basa puramente sulle proprietà dei componenti JTAG, sulle connessioni della scheda e – nel caso di XJTAG – sul funzionamento dei componenti logici presenti nel circuito. Il secondo modo, invece, amplia la copertura di test utilizzando i componenti abilitati al JTAG per comunicare con altri componenti non-JTAG, come ad esempio le RAM DDR e le flash.

Cos'è un test di connessione JTAG?

Un test di connessione JTAG verifica che su una scheda elettronica le connessioni attorno ai dispositivi abilitati al JTAG rispettino quelle specificate nel progetto.

Se da progetto due pin con accesso JTAG devono essere connessi, il test assicurerà che un pin possa essere controllato dall’altro. Quando, invece, i pin JTAG non devono essere connessi tra loro, essi vengono testati per individuare eventuali guasti di cortocircuito pilotando un pin e verificando che i valori forzati non siano letti sugli altri pin.

Resistenze di pull-up/pull-down mancanti e corti verso masse e alimentazioni possono essere individuati dal test di connessione, come anche eventuali problemi che riguardano componenti logici il cui comportamento può essere descritto in una tabella di verità.

XJTAG genera automaticamente i vettori necessari per eseguire un test di connessione basato sulla netlist di una scheda e sulle informazioni relative alle funzionalità JTAG dei dispositivi abilitati.

E per i dispositivi che non sono abilitati al JTAG?

Mentre i dispositivi principali, come i processori e le FPGA, sono normalmente abilitati al JTAG, su ogni scheda elettronica ci saranno molti altri componenti che non lo sono. DDR, SDRAM, SRAM, flash, Ethernet PHY, sensori di temperatura SPI e I2C, clock real time, ADC e DAC sono solo alcuni esempi di tali dispositivi.

Il test di connessione fornirà un’ottima copertura per i guasti di cortocircuito sulle net che collegano questi componenti non-JTAG a quelli JTAG. Tuttavia, questo test non è in grado di verificare eventuali guasti di circuito aperto sia sul componente JTAG che su quello non JTAG.

Per aggiungere questa copertura sugli eventuali circuiti aperti è necessario interagire con il componente non-JTAG sfruttando le funzionalità boundary scan fornite dal componente JTAG. Quindi, se la comunicazione tra i due componenti può essere verificata, potremo scartare guasti dati da circuiti aperti. Questo tipo di test può essere molto semplice (come ad esempio accendere un LED sulla scheda e chiedere ad un operatore di verificarne il funzionamento), oppure più complesso (come ad esempio scrivere dati nell’array di memoria di una RAM e poi farne la lettura).

Quanto lavoro richiede creare un sistema di test JTAG?

Utilizzando le librerie fornite da XJTAG per i componenti standard non-JTAG è possibile ottenere un set di test immediatamente funzionanti sulla tua scheda, senza lo sviluppo di alcun codice. I file di libreria contengono modelli per tutti i tipi di dispositivi non-JTAG, da semplici resistenze e buffer a componenti più complessi come le memorie DDR3. Poiché il boundary scan isola il controllo dei pin sui dispositivi JTAG dalla loro effettiva funzionalità, lo stesso modello può essere utilizzato indipendentemente dal componente JTAG che controlla una determinata periferica.

La maggior parte delle schede contiene già connettori JTAG per la programmazione o il debug, quindi non sono richiesti requisiti di progettazione aggiuntivi per utilizzare questa tecnologia.

Dove posso ottenere le informazioni in merito al JTAG implementato sui miei componenti?

Per eseguire il test boundary scan è necessario avere alcune informazioni in merito all’implementazione del JTAG sui componenti abilitati. Tali informazioni sono contenute nei file BSDL (Boundary Scan Description Language) rilasciati per questi componenti. I file BSDL devono essere messi a disposizione dal fornitore del silicio per far sì che un componente sia conforme con lo Standard IEEE 1149.1.

Il test JTAG viene utilizzato esclusivamente in produzione?

Niente affatto! Uno dei vantaggi principali del boundary scan è che l’unico hardware richiesto per il test è un controller JTAG. Altre tecnologie di test utilizzate in produzione, come le macchine a sonde mobili (flying probe), l’ispezione ottica, i raggi X o il letto d’aghi hanno bisogno di apparecchiature di test specializzate che di solito non sono disponibili in laboratorio per gli sviluppatori.

L’utilizzo del boundary scan durante la fase di board bring-up può aiutare a chiarire dei dubbi; gli ingegneri possono, infatti, testare i prototipi per individuare eventuali difetti di fabbricazione prima del test di sistema, e anche prima che il firmware sia disponibile. I sistemi di test sviluppati in questa fase iniziale del ciclo di vita del prodotto possono essere facilmente riutilizzati ed eventualmente estesi per la produzione.

Perché dovrei utilizzare il JTAG / boundary scan per testare le mie schede?

Tre semplici lettere – BGA

Un numero sempre più elevato di componenti è oggi fornito in package BGA (Ball Grid Array). Ogni componente BGA su una scheda impone severe restrizioni per i test che possono essere eseguiti usando macchine tradizionali, come il letto d’aghi o le sonde mobili.

Utilizzando una semplice interfaccia a quattro pin, il JTAG / boundary scan consente di controllare e monitorare i segnali sui componenti abilitati, anche senza alcun accesso fisico diretto.

Altre tre lettere – NRE

I costi non ricorrenti (NRE) per lo sviluppo e la costruzione delle fixture di test molto spesso risultano proibitivamente elevati. In molti casi l’utilizzo del test JTAG / boundary scan potrebbe addirittura abolire la necessità di una fixture, mentre in altri casi quest’ultima può essere ampiamente semplificata con un conseguente significativo risparmio dei costi.

Tempi di test più brevi

Per schede con bassi volumi di produzione è sempre stato difficile giustificare il costo dello sviluppo di un banco di test. In questi casi un’alternativa potrebbe essere il test a sonde mobili ma, tuttavia, i tempi di test con questa tecnologia tendono ad essere molto elevati. Il JTAG / boundary scan consente di abbattere i tempi di test evitando un ingente costo fisso per la fixture.

Costi ridotti per lo sviluppo del test

Poiché i diversi processori / FPGA interagiscono con le periferiche in modi diversi, il test funzionale tradizionale richiede costosi sviluppi specifici per ogni scheda. Il JTAG / boundary scan riduce notevolmente tali costi di sviluppo poiché fornisce un’interfaccia semplificata per controllare i pin di I/O utilizzati per interagire con le varie periferiche. Questa interfaccia standard, che è la stessa per tutti i dispositivi abilitati al JTAG, garantisce che dei modelli generici di test possano essere utilizzati durante la realizzazione degli apparati di test.

Uno strumento unico per il test e la programmazione

Il JTAG viene spesso già utilizzato per uno step in produzione: la programmazione. Utilizzando il JTAG anche per il test boundary scan è possibile ridurre il numero di passaggi e le operazioni di gestione nel processo produttivo.

Test a livello di produzione disponibili sulle scrivanie dei tecnici per la verifica dei prototipi

Le tecnologie tradizionali di test richiedono attrezzature molto elaborate e costose. L’unica apparecchiatura di test necessaria per il test JTAG / boundary scan è un controller JTAG, il controller XJLink2 di XJTAG, ha una dimensione simile ad un mouse per PC.

Ottima diagnostica dei guasti

Il JTAG / boundary scan, a differenza del test funzionale, fornisce informazioni molto precise in merito ai guasti rilevati sulla scheda, e ciò facilita una rapida riparazione. XJTAG fornisce anche la possibilità di visualizzare sia la posizione fisica di un guasto sul layout della scheda sia l’area del circuito in cui il guasto è localizzato sullo schema elettrico.

Recuperare le schede fuori uso per le quali il test funzionale non sarebbe sufficiente

I test JTAG / boundary scan possono essere eseguiti su qualsiasi scheda con un’interfaccia JTAG funzionante. I test funzionali tradizionali non possono essere eseguiti se il firmware sulla scheda non si avvia. Per semplici errori sulle periferiche principali, come le RAM o i clock, il test funzionale non sarebbe in grado di fornire alcuna informazione diagnostica, mentre essi sarebbero individuati facilmente utilizzando il JTAG.

- JTAG è più che debug e programmazione

- Come il JTAG / boundary scan è utilizzato per testare una scheda

- Cos'è un test di connessione JTAG?

- E per i dispositivi che non sono abilitati al JTAG?

- Quanto lavoro richiede creare un sistema di test JTAG?

- Dove posso ottenere le informazioni in merito al JTAG implementato sui miei componenti?

- Il test JTAG viene utilizzato esclusivamente in produzione?

- Perché dovrei utilizzare il JTAG / boundary scan per testare le mie schede?

- Altre tre lettere – NRE

- Tempi di test più brevi

- Costi ridotti per lo sviluppo del test

- Uno strumento unico per il test e la programmazione

- Test a livello di produzione disponibili sulle scrivanie dei tecnici per la verifica dei prototipi

- Ottima diagnostica dei guasti

- Recuperare le schede fuori uso per le quali il test funzionale non sarebbe sufficiente

Pronto ad iniziare?

Guarda XJTAG in azione

I nostri esperti saranno lieti di mostrarti come gli strumenti di XJTAG possono aiutarti a diagnosticare i guasti sulla tua scheda elettronica e a ridurre i tempi di sviluppo dei test e di riparazione.

Hai domande? Contattaci!

Siamo qui per aiutarti. Inviaci un messaggio e uno dei nostri specialisti del test ti risponderà il prima possibile.

Ottieni una configurazione gratuita

Prova gratuitamente il sistema XJTAG con tutte le sue funzionalità per 30 giorni e ottieni anche una configurazione gratuita del primo progetto di test per la tua scheda, senza nessun obbligo di acquisto.