Использование возможностей технологии пограничного сканирования (Boundary Scan) в JTAG-совместимых микросхемах даёт много преимуществ при отладке прототипа и/или при тестировании печатных плат на производстве. XJTAG® DFT Ассистент для Altium Designer® выполняет проверки корректности JTAG цепи еще на стадии проектирования.

Выгоды

- Анализ DFT непосредственно в Altium Designer

- Устранение ошибок на этапе проектирования схемы, до разводки платы

- Визуальная индикация доступных для тестирования компонентов

- Правильная реализация JTAG цепи повышает покрытие

- Правильная реализация JTAG цепи повышает эффективность тестирования на производстве

- Экспорт данных в среду разработки тестирования XJDeveloper (требуется отдельная лицензия на продукты фирмы XJTAG)

На этапе проектирования

При реализации JTAG цепи в проекте печатной платы желательно выдерживать ряд параметров. Получить максимальные преимущества от технологии пограничного сканирования (Boundary Scan), реализованной в большинстве современных микросхем, таких так микропроцессоры, микроконтроллеры, сигнальные процессоры, ПЛИС и так далее, можно только если JTAG це́пи подключены и согласованы правильно. Соблюдение правил проектирования повышающих тестируемость платы обозначается условным обобщённым названием Design for Test (DFT).

Наглядная индикация того, какие микросхемы на плате могут быть протестированы через пограничное сканирование (Boundary Scan) также очень важна, так как позволяет внести изменения в проект для увеличения тестового покрытия на ранних стадиях проектирования.

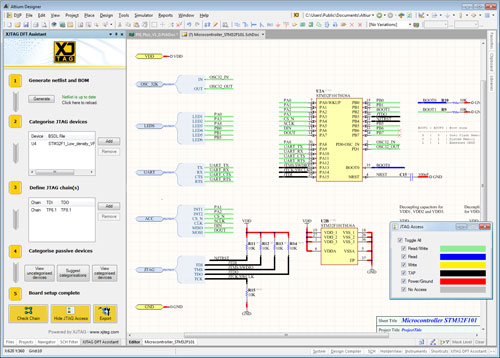

XJTAG DFT Ассистент помогает автоматизировать эти процессы, подключая импортированные BSDL файлы к соответствующим компонентам на схеме, подготавливая тем самым основу для анализа правильности подключения JTAG цепи. Комбинационная логика и пассивные компоненты в составе JTAG цепи также могут быть обнаружены и классифицированы. Таким образом вся JTAG цепь, со всеми входящими в её состав компонентами, может быть проанализирована на предмет правильности подключения еще на этапе проектирования схемы. Визуализация доступности компонентов для тестирования непосредственно в схеме позволяет зрительно оценить тестовое покрытие и способы его улучшения.

Инсталляция XJTAG DFT Ассистент в Altium Designer означает возможность для разработчиков находить и исправлять потенциальные проблемы в JTAG цепях непосредственно в схеме, до начала проектирования топологии, что экономит время и стоимость проектирования.

Программное дополнение для Altium Designer под названием XJTAG DFT Ассистент включает два модуля: “XJTAG Chain Checker” и “XJTAG Access Viewer”.

XJTAG Chain Checker

Модуль Chain Checker анализирует нетлист и находит готовые XJTAG цепи. При этом находятся ошибки и потенциальные ошибки (предупреждения) в JTAG цепях, включая:

- Ошибки подключения, когда один из сигнальных контактов интерфейса JTAG Test Access Point (TAP) подключён к неправильному контакту JTAG-совместимой микросхемы.

- Предупреждения по согласованиям, если какой-либо TAP сигнал не согласован должным образом

- Ошибки по согласованиям, если неправильно расставлены подтягивающие резисторы и/или остались “висящие” цепи.

XJTAG Access Viewer

XJTAG DFT Ассистент находит, также, микросхемы без поддержки JTAG, которые тем не менее можно протестировать через JTAG. Эту информацию можно при помощи XJTAG Access Viewer наложить непосредственно на схему, что позволяет в процессе проектирования схемы сразу видеть, какие компоненты могут быть протестированы. Такая визуализация тестового покрытия позволяет оценить влияние производимых изменений на тестируемость платы, наблюдать увеличение тестового покрытия при внедрении новых цепей.

Весь процесс DFT анализа управляется расширением XJTAG DFT Ассистент для Altium Designer. Собираемая информация может быть экспортирована в виде проекта для XJDeveloper, который затем может быть использован как основа для последующей разработки проекта тестирования на основе контроллеров XJLink2, когда плата будет изготовлена.

XJTAG Access Viewer наглядно показывает тестовое покрытие

Возможности

- Предварительный JTAG DFT анализ

- Автоматический импорт нетлиста из Altium Designer

- JTAG Access Viewer — визуальная индикация доступных для тестирования цепей непосредственно в схемотехническом редакторе

- Chain Checker — анализ правильности формирования JTAG цепей и вывод найденных ошибок

- Три категории ошибок: ошибки при подключении (connection), ошибки в согласованной нагрузке (termination) и ошибки в согласовании подтягивающими резисторами (compliance)

- Отображение тестируемых цепей определёнными цветами

- Помощник в классификации JTAG-несовместимых компонентов

- Экспорт результатов в XJDeveloper, среду подготовки проекта тестирования прототипа и/или на производстве