XJTAG® DFT Assistant for Altium Designer®

Run Design For Test (DFT) Checks at the Schematic Capture stage

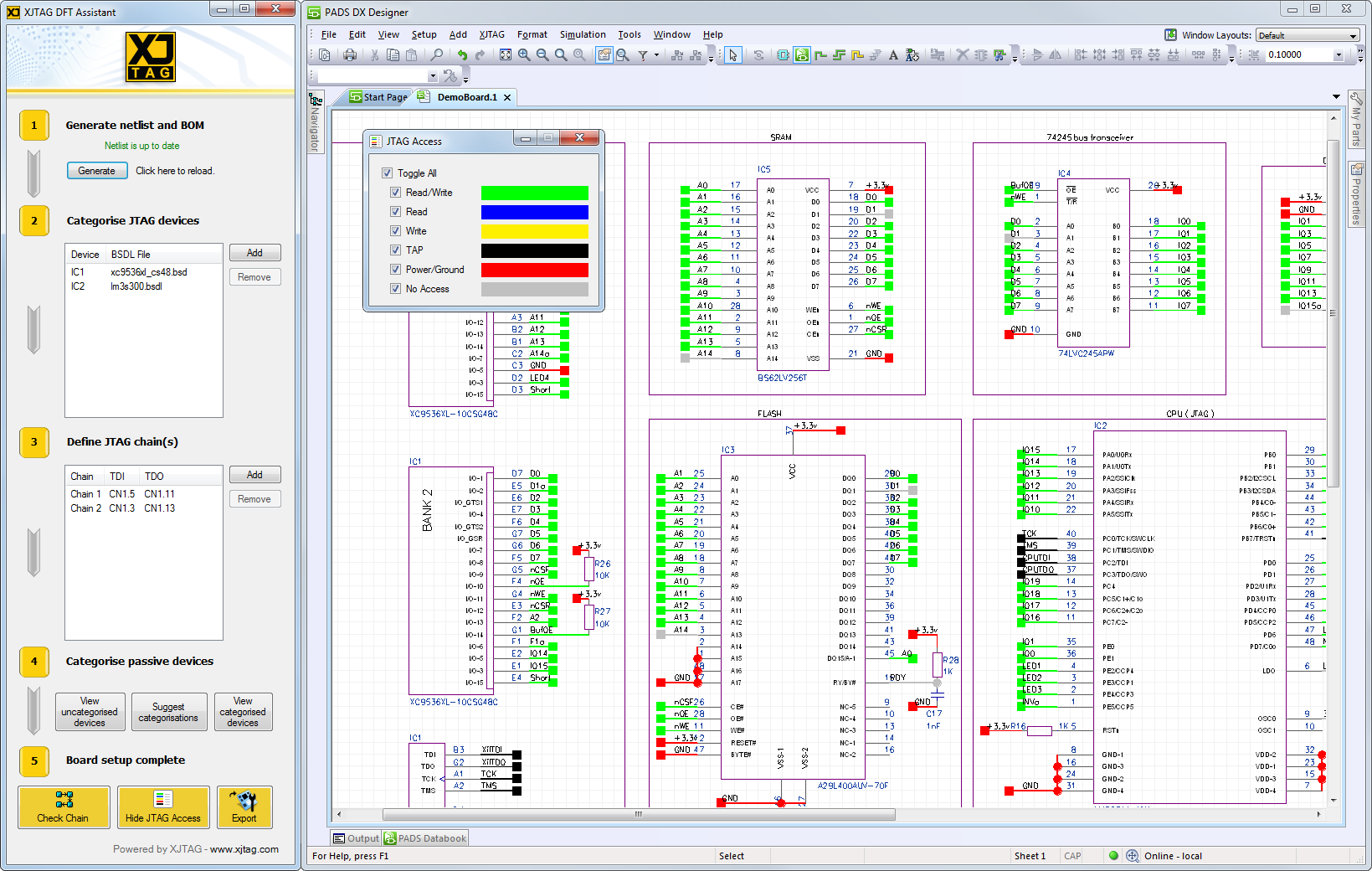

The XJTAG DFT Assistant is a free software extension developed by XJTAG® for the Altium Designer unified development environment. Comprising much of the setup stages found in XJDeveloper, along with additional and unique functionality, it allows engineers to conduct Design For Test (DFT) checks of a design during the schematic capture stage.

Features

- Fully integrated into Altium Designer*

- Assisted board setup to carry out a JTAG DFT analysis

- Automatic import of netlist from Altium Designer

- Includes a JTAG access viewer that overlays testable nets in a design on a schematic diagram

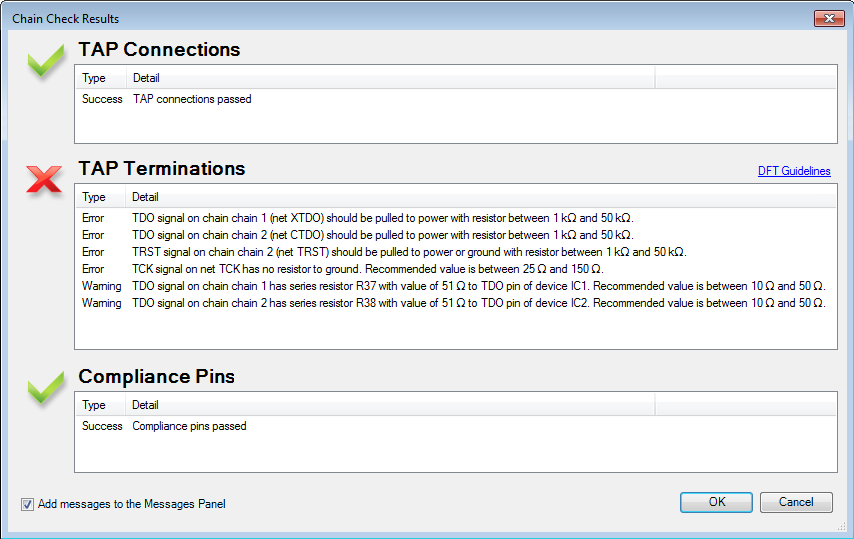

- Analysis of results from the XJTAG Chain Checker tool clearly identifies potential errors in the chain(s)

- Provides three categories of error: connection, termination and compliance

- Shows testable nets using colour-coded connections

- Assisted categorisation of logic and passive devices, to extend scan chains

- Export projects for use in XJDeveloper

*Please note this extension requires Altium 15 or later and is NOT compatible with versions later than 24.7.

The DFT Assistant identifies potential problems early in the design cycle by validating the correct implementation of boundary scan chains, as well as compliance to Design For Test best-practices. It comprises the XJTAG Chain Checker and the XJTAG Access Viewer.

XJTAG Chain Checker

The XJTAG Chain Checker tool works in much the same way as setting up JTAG chains in an XJDeveloper project, by analysing the netlist and finding a routable scan chain. It also offers a unique DFT feature; checking that the TAP signals are correctly terminated.

XJTAG Chain Checker identifies potential errors and warnings found on JTAG chains, including:

- Connection errors if any of the JTAG Test Access Point (TAP) signals are connected to the wrong pin(s) on a JTAG-compliant IC.

- Termination warnings if any of the TAP signals are not terminated as recommended.

- Compliance pin errors if they are incorrectly pulled high or low, or are left floating.

XJTAG Access Viewer

The XJTAG DFT Assistant extension also identifies the extent of JTAG access across an entire schematic. This is overlaid on to the schematic using the XJTAG Access Viewer, allowing designers to understand their test coverage at an early stage in the design. By visualising the extent of test coverage, engineers are able to see the impact design changes have on their test coverage, seeing it increase as additional nets on the board are made accessible to boundary scan.

The entire process of DFT analysis is handled by the extension and reported back within Altium Designer. The information gathered can also be exported as an XJDeveloper project, where it can be imported and used as the basis for further test development, using an XJLink2 controller for testing the PCB once it has been manufactured.