XJAnalyser Module

Add visual analysis and debug capabilities to your XJTAG tools

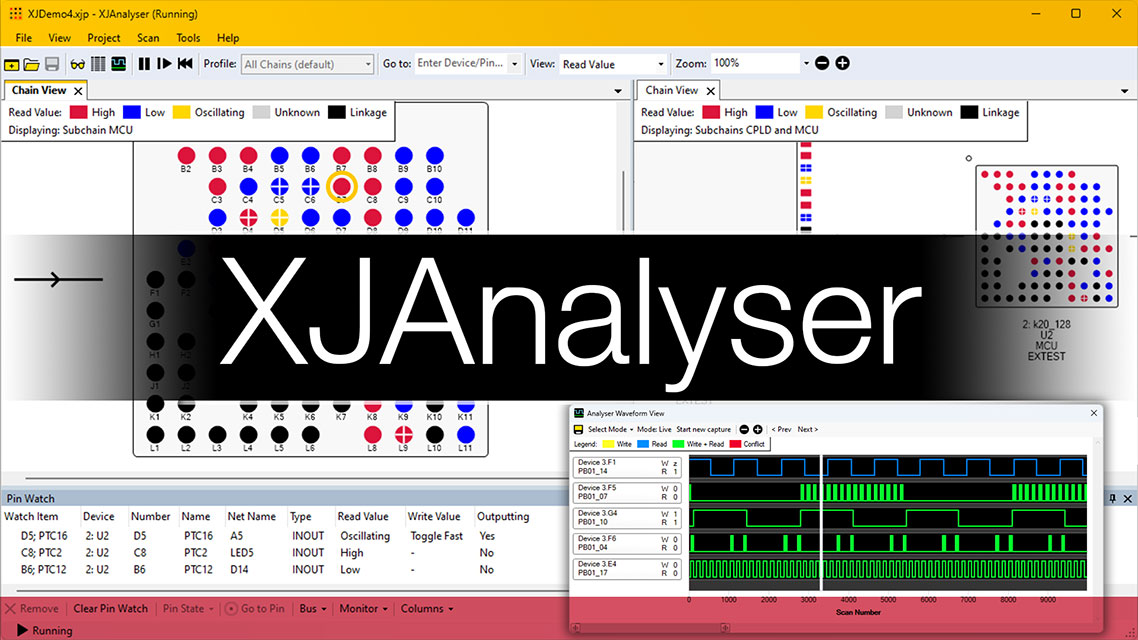

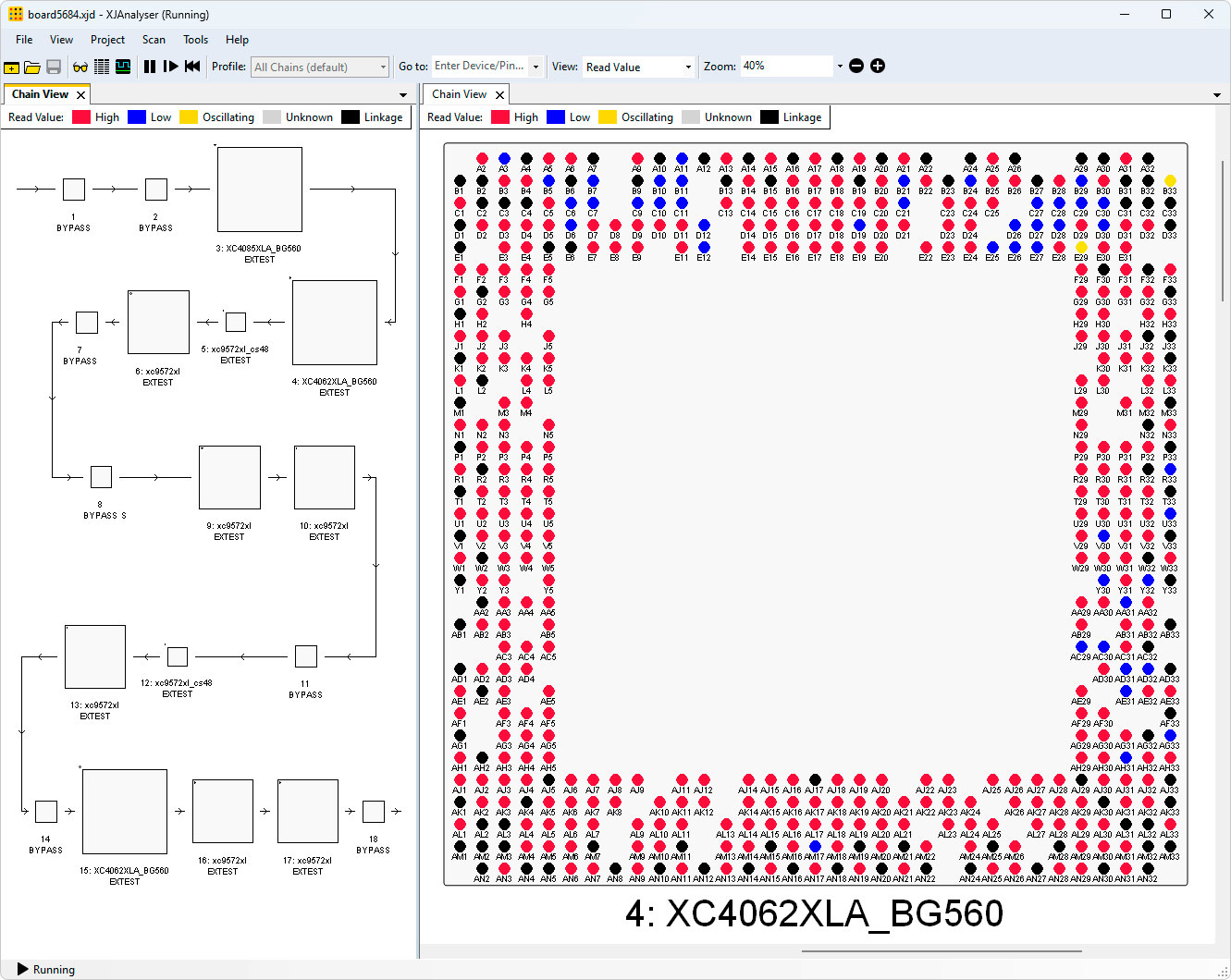

XJTAG’s XJAnalyser module is a powerful tool for real-time circuit visualisation and debugging. It provides a graphical view of JTAG chains, giving you control and visibility, on a pin-by-pin basis, of both pin value (digital high or low) and output state (driving or set to high-impedance).

XJAnalyser Module provides an intuitive interface for setting output pin states and values, and reading input values from a circuit in near real time. The default view uses colour coding on a visual representation of devices in the circuit, but tables can also be used as can a logic analyser style view.

The module is available:

- as an add-on to XJDeveloper, where it gives access to the Analyser screen and to the XJInvestigator application

- as an add-on to XJRunner, where it gives the ability to run the XJInvestigator application, XJTAG’s repair-focused test and debug environment for fault analysis

- as a standalone licence, where it gives the ability to run the XJAnalyser application which in addition to providing graphical JTAG chain control/view functionality also has the facility to run SVFand STAPL / JAM files.

XJInvestigator is a repair focused, integrated test and debug environment for fault analysis, combining the test capabilities of XJRunner and XJAnalyser with additional diagnostic functionality.

XJAnalyser Module Benefits

Gives access to components that can’t be probed

Read and write access pins on BGA and fine-pitch devices or where test points aren’t available.

Ready to use within minutes

Connecting the standalone XJAnalyser app to the JTAG chain is very simple.

Quickly debug and verify manufacturing faults

Allows you to increase yields by quickly confirming test results or checking a fix.

Control and monitor the pins on JTAG devices

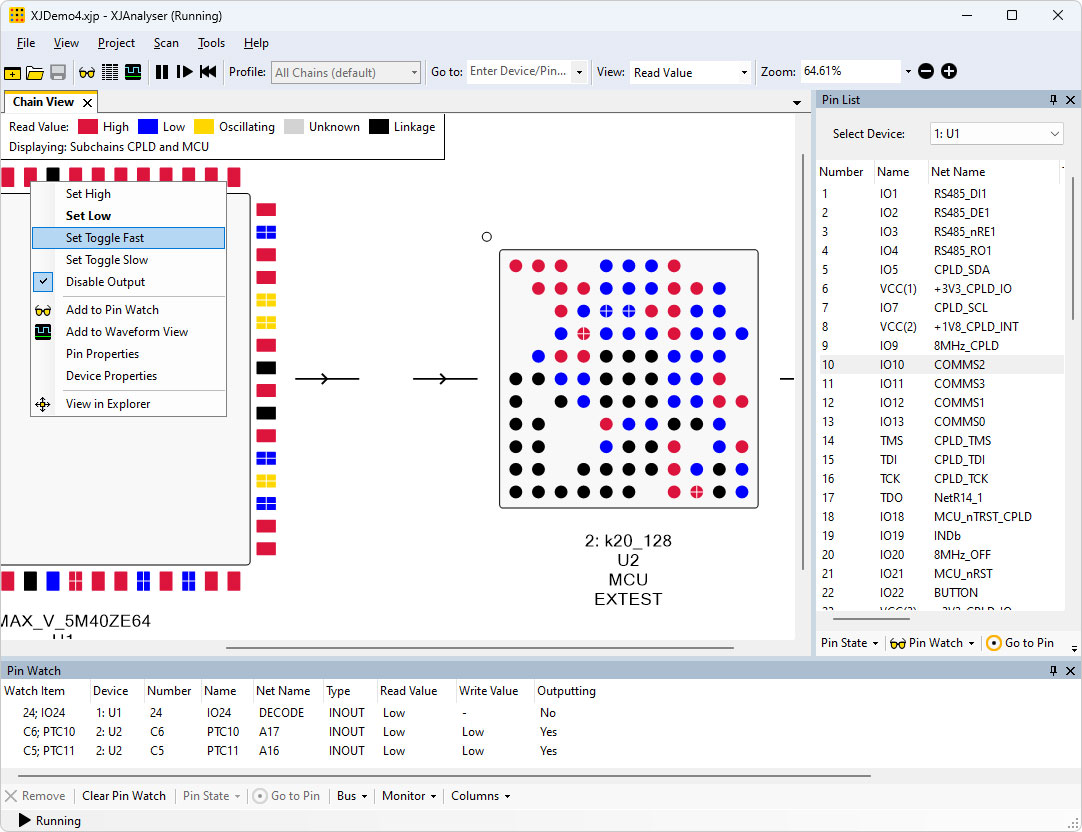

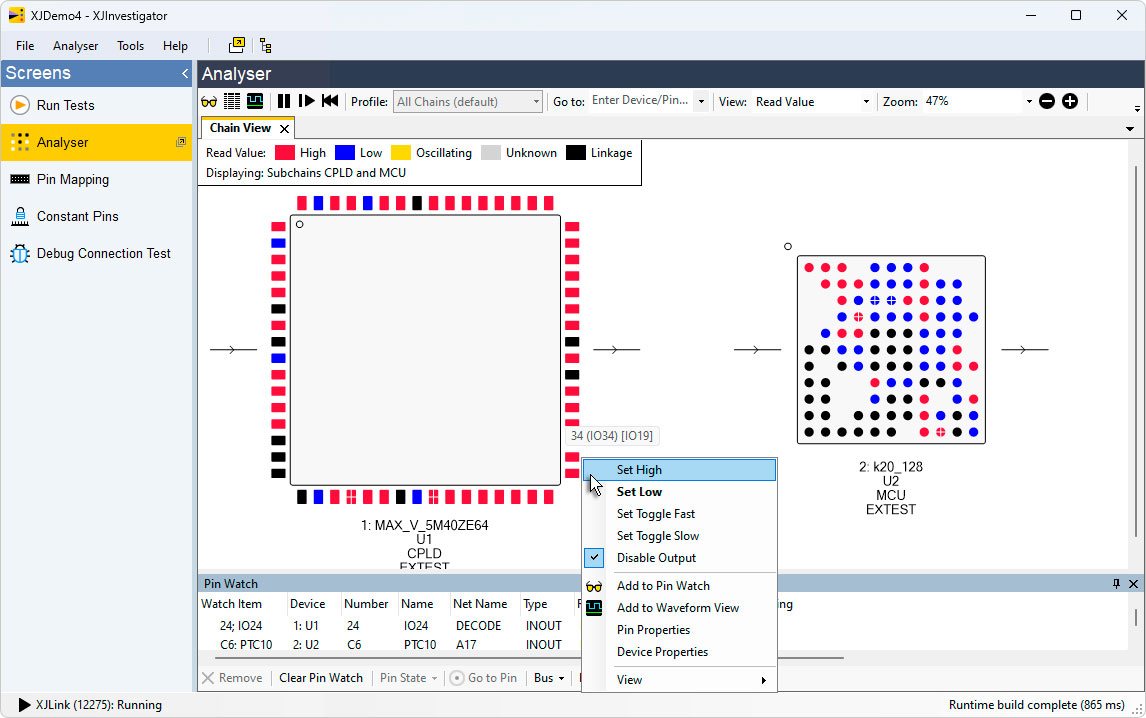

Pin values can be set high or low, or into slow or fast toggle, all at a click of the mouse. The pin colours then indicate their values in real time.

You can place pins in a ‘watch window’ to make it easy to see their changes amongst all of the pins around them on a device, or configure the watch window to automatically add any pins which change value in the circuit.

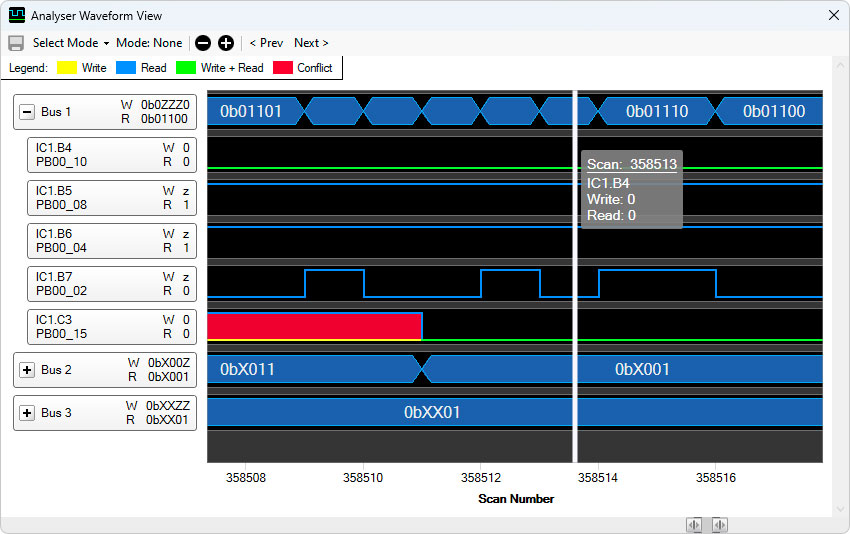

Buses can be built from pins in the watch window; you can then write a value to the bus to set all of those pins at once.

Visualise the pin states intuitively

View the devices in the JTAG chains graphically, with user-definable zoom levels. You can also split the screen and view different parts of the circuit at different magnifications.

Observe pin states by looking at a table of pins and values, or graphically with the colours on a representation of the JTAG devices showing you the current state of pins. Additionally, the Waveform View captures and displays the digital signal levels and transitions of JTAG chain data, showing you the state of selected pins over a period of time.

Detect and investigate specific conditions or events by using the triggering capabilities of the waveform view, which can greatly improve an engineering team’s ability to capture key information and identify intermittent faults.

Take control of the circuit

The XJAnalyser module can either perform continuous write-read JTAG cycles, giving instant feedback on signal changes, or it can iterate single cycles under user control, allowing manual changes between each cycle.

You can run SVF and STAPL / JAM files that apply to any sequence of devices in your circuit.

The Golden Board comparison feature can capture the values being driven onto the JTAG devices of a known good board. These values can then be used to identify differences between a board exhibiting unexpected behaviour and the reference board.

XJAnalyser Features

Graphical device view

Easily understandable way to view many pins at once

Waveform view

Shows pin values over time in logic analyser style view

Pin Watch

Monitor specific pins or look for pins changing value

Drive values to the circuit

Set a pins or groups of pins high or low with just a click

Real time display

Set or read pin values across the circuit

XJIntegration available

Use XJAnalyser module features via API from other software

Trace faults

Assists in tracing signals and in locating short circuit and open circuit faults

Program JTAG devices

Program devices by running SVF and STAPL files within XJAnalyser

No-netlist operation

XJAnalyser standalone application only requires BSDL files to get up and running

XJInvestigator Features

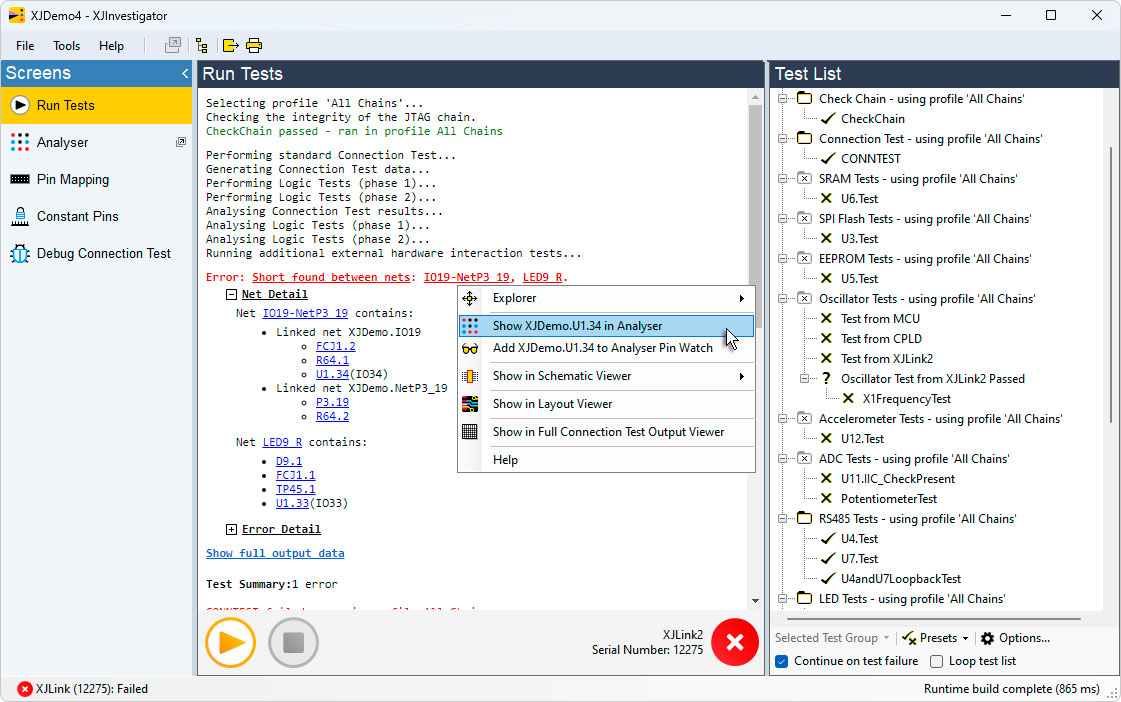

In addition to the features in XJAnalyser, described above, the XJInvestigator application, designed to provide a repair-focused environment for XJDeveloper / XJRunner tests, brings:

Full XJRunner environment

Perform all the production line tests exactly as XJRunner does, including logging results

In-system programming

Program flash, FPGA, CPLD and EEPROMs (including using XJFlash)

Layout Viewer*

Shows the physical location of faulty nets, pins and components

Schematic Viewer*

Shows the circuit design and can highlight areas around faults

Debug JTAG chain problems

The Pin Mapping screen from XJDeveloper can be used to debug and diagnose issues with setup and signal integrity

Debug broken chain errors in connection test

The Debug Connection Test screen from XJDeveloper is available to investigate unexpected broken chain errors

* The Layout and Schematic Viewers are only available if you opt to include the required information in the XJPack file when exporting it from XJDeveloper.

Improve your diagnostic capabilities in production repair

Not only can you reproduce XJRunner’s error reports, you can also take direct control of the pins/balls on the JTAG devices from the Analyser screen and run extra diagnostic functions not normally available on the production line. You can then visualise any fault on both the schematic and layout of the board using the integrated viewers.

If the production line tests cannot be run on a board due to problems with the scan chain then the built-in JTAG Chain Debugger helps you quickly identify these faults so normal testing can continue.

Take direct control of JTAG devices

Simple ad-hoc tests can be implemented very quickly by controlling and monitoring signals on the board from your JTAG-enabled devices, even BGAs. On the Analyser screen, pin values can be set to toggle or to be driven high or low. The values of pins read from the board are shown in a simple colour-coded display.

Flexible interface

In XJInvestigator you can keep the test results visible while you are using Analyser and the other debugging features such as the Layout and Schematic Viewers, which helps further streamline and simplify the debugging process.

Layout & Schematic Viewers included

By showing both the physical and logical organisation of a board, the Layout Viewer and Schematic Viewer* can be used to help understand and locate faults.

* The Layout and Schematic Viewers are only available if you opt to include the required information in the XJPack file when exporting it from XJDeveloper.

Simple, powerful and flexible diagnostic testing

XJInvestigator extracts all the information required to test and debug your boards from the same encrypted XJPack file that is used by XJRunner. To ensure consistency in the testing process the predefined test functions cannot be modified however XJInvestigator offers the extra flexibility and configuration options needed to help you to track down faults.

When a problem has been identified with a board you can select to run individual tests, sets of tests or additional functions not included in production testing. The tests can also be run continuously to help diagnose particularly tricky or intermittent problems.

Recommended system requirements

Intel® Core i3, i5, i7 processor or equivalent (any generation).

Microsoft® Windows® 10 1607 and later (32 or 64 bit), or Windows 11.

8 GB of RAM.

Flexible Licensing Options

Hardware licence

Held in the JTAG controller so you can install XJTAG on any number of PCs.

Network licence

Held on a networked license server available from anywhere in the world.

Configure your products

Take a Free Trial of XJTAG software & hardware products

30 days of discovery with full features

Any questions? Contact us